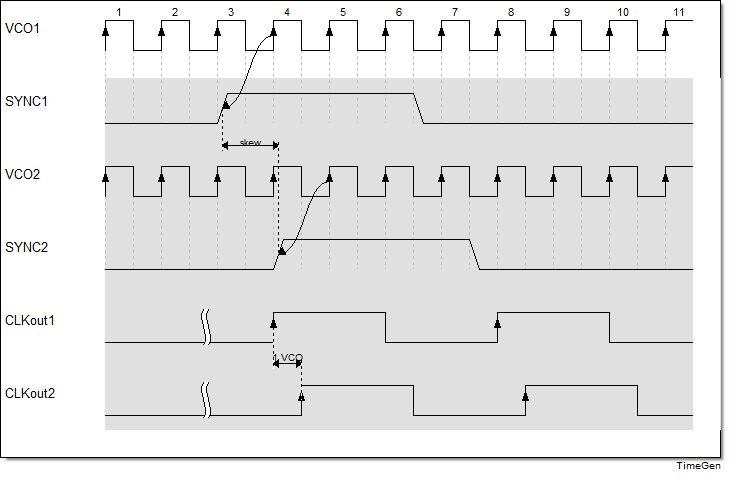

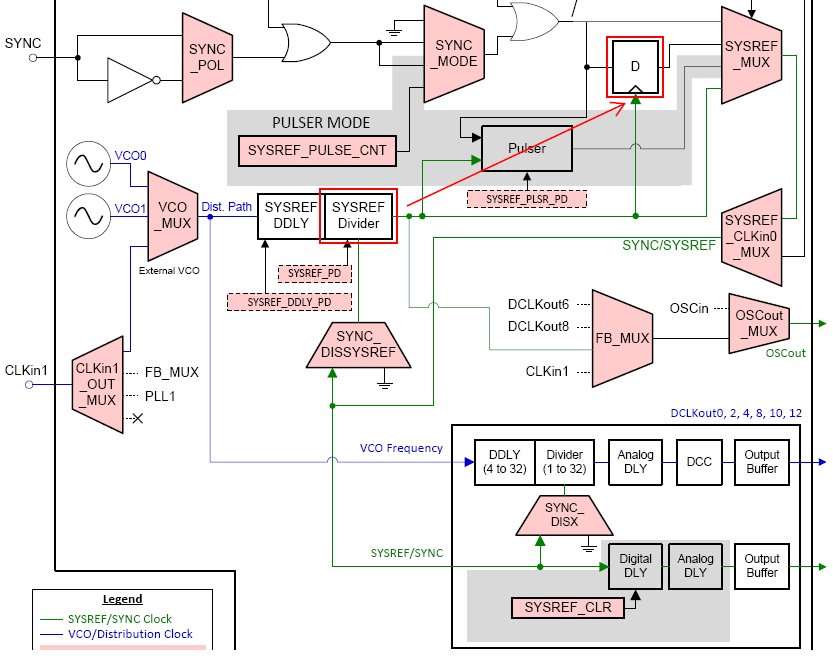

I would like to sync multiple LMK04828's outputs on separate boards, a reference 20MHz is fan-out to each OSCin of LMK04828, Can a common external SYNC signal synchronize all outputs??? can external input SYNC synchronize multiple LMK04828's output dividers??? what the phase relationship between OSCin and SYNC input???

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.