Hello,

In my design I need to supply clocking for a JESD204B interface by using a Arria V FPGA to configure lmk04821.

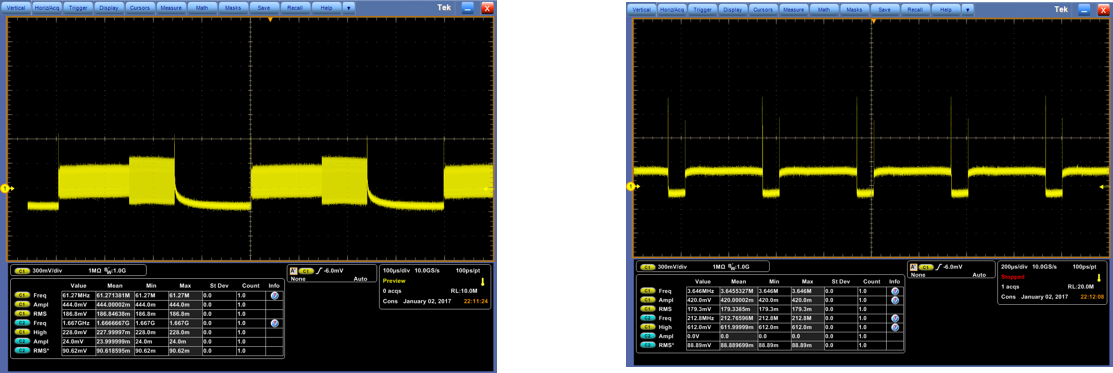

According to Key Points to Setting up SYNC & SYSREF on LMK0482x with CodeLoader.pdf, i write a configuration file as below but the clock output is wrong.(left is dclk output and right is sysref outout)

Can you tell me whats wrong and how can i solve my problem? Thank you.

The configuration sequence is shown as below:

localparam R0 = 24'h0000_80,

R1 = 24'h0000_00,

R2 = 24'h0002_00,

//-----------step 1 Setup Clock Outputs-------------------------//

//Set SDCLKoutY_MUX = SR Select SYSREF source for SDCLKoutY.//

//Set DCLKoutX_DDLY_PD = 0 & SYSREF_DDLY_PD = 0//

R3 = 24'h0100_08,

R4 = 24'h0101_55,

R5 = 24'h0103_01,

R6 = 24'h0104_22,

R7 = 24'h0105_00,

R8 = 24'h0106_71,

R9 = 24'h0107_01,

R10 = 24'h0108_0A,

R11 = 24'h0109_55,

R12 = 24'h010B_00,

R13 = 24'h010C_22,

R14 = 24'h010D_00,

R15 = 24'h010E_71,

R16 = 24'h010F_11,

R17 = 24'h0110_0A,

R18 = 24'h0111_55,

R19 = 24'h0113_00,

R20 = 24'h0114_22,

R21 = 24'h0115_00,

R22 = 24'h0116_71,

R23 = 24'h0117_11,

R24 = 24'h0118_08,

R25 = 24'h0119_55,

R26 = 24'h011B_00,

R27 = 24'h011C_22,

R28 = 24'h011D_00,

R29 = 24'h011E_71,

R30 = 24'h011F_11,

R31 = 24'h0120_08,

R32 = 24'h0121_55,

R33 = 24'h0123_00,

R34 = 24'h0124_02,

R35 = 24'h0125_00,

R36 = 24'h0126_71,

R37 = 24'h0127_10,

R38 = 24'h0128_08,

R39 = 24'h0129_55,

R40 = 24'h012B_00,

R41 = 24'h012C_02,

R42 = 24'h012D_00,

R43 = 24'h012E_79,

R44 = 24'h012F_00,

R45 = 24'h0130_08,

R46 = 24'h0131_55,

R47 = 24'h0133_00,

R48 = 24'h0134_22,

R49 = 24'h0135_00,

R50 = 24'h0136_71,

R51 = 24'h0137_01,

R52 = 24'h0138_25,

R53 = 24'h0139_00,

R54 = 24'h013A_01,

R55 = 24'h013B_00,

R56 = 24'h013C_00,

R57 = 24'h013D_08,

R58 = 24'h013E_03,

R59 = 24'h013F_00,

R60 = 24'h0140_0D,

R61 = 24'h0141_00,

R62 = 24'h0142_00,

R63 = 24'h0143_01,

R64 = 24'h0144_FF,

R65 = 24'h0145_7F,

R66 = 24'h0146_18,

R67 = 24'h0147_1A,

R68 = 24'h0148_02,

R69 = 24'h0149_42,

R70 = 24'h014A_02,

R71 = 24'h014B_16,

R72 = 24'h014C_00,

R73 = 24'h014D_00,

R74 = 24'h014E_C0,

R75 = 24'h014F_7F,

R76 = 24'h0150_03,

R77 = 24'h0151_02,

R78 = 24'h0152_00,

R79 = 24'h0153_00,

R80 = 24'h0154_78,

R81 = 24'h0155_00,

R82 = 24'h0156_03,

R83 = 24'h0157_00,

R84 = 24'h0158_96,

R85 = 24'h0159_00,

R86 = 24'h015A_03,

R87 = 24'h015B_D4,

R88 = 24'h015C_20,

R89 = 24'h015D_00,

R90 = 24'h015E_00,

R91 = 24'h015F_0B,

R92 = 24'h0160_00,

R93 = 24'h0161_05,

R94 = 24'h0162_A4,

R95 = 24'h0163_00,

R96 = 24'h0164_00,

R97 = 24'h0165_0A,

R98 = 24'h0174_05,

R99 = 24'h017C_15,

R100= 24'h017D_33,

R101= 24'h0166_00,

R102= 24'h0167_00,

R103= 24'h0168_0A,

R104= 24'h0169_59,

R105= 24'h016A_20,

R106= 24'h016B_00,

R107= 24'h016C_00,

R108= 24'h016D_00,

R109= 24'h016E_13,

R110= 24'h0173_00,

R111= 24'h1FFD_00,

R112= 24'h1FFE_00,

R113= 24'h1FFF_53,

//-----------step 2 Power up SYSREF and prepare SYNC path to Dividers-------------------------//

R114= 24'h0143_11,//SYNC_EN = 1 SYNC_MODE = Sync Pin;SYSREF_MUX = Normal SYNC

R115= 24'h0140_08,//SYSREF_PD = 0 SYSREF_PLSR_PD = 0

R116= 24'h0144_00,//SYNC_DISSYSREF = 0 SYNC_DISX = 0

R117= 24'h0106_70,//SDCLKoutY_PD = 0

R118= 24'h010E_70,

R119= 24'h0116_70,

R120= 24'h011E_70,

R121= 24'h0126_70,

R122= 24'h012E_78,

R123= 24'h0136_70,

//-----------step 3 Reset SYSREF -------------------------//

R125= 24'h0143_91, //SYSREF_CLR = 1

R126= 24'h0143_11, //SYSREF_CLR = 0

//-----------step 4 Reset SYSREF -------------------------//

R127= 24'h0143_31,//SYNC_POL=1

R128= 24'h0143_11,// SYNC_POL=0

//-----------step 5 Disable SYNC/SYSREF Path from Resetting Dividers-------------------------//

R129= 24'h0144_FF, //SYNC_DISSYSREF = 1;SYNC_DISX = 1

//----------- step 6 Set Desired SYSREF Generation Mode - Pulsed -------------------------//

R130= 24'h0139_03,// SYNC_MODE = SPI (Pulser)

R131= 24'h0143_11;//SYNC_MODE = Pin (Pulser)