Hi,

QUESTION 1

LMK04610 is used to generate a 200MHz LVDS (4-mA HSDS or 6-mA HSDS) system clock to KINTEX7 160T FPGA. The output clock generated is having much higher differential output voltage swing than normal LVDS specification so what on board termination have to set at the input of KINTEX7 FPGA.

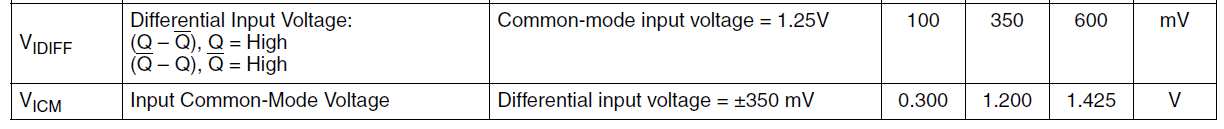

The FPGA LVDS specification for the clock input is as follows

QUESTION 2

A 100MHz LVCMOS VCXO is connected to the OSCIN pin of LMK04610. The buffered copy of this 100MHz LVCOMS clock is taken out at OSCOUT pin for power on FPGA system clock.

Then what to do with OSCOUT* pin (NC or Ground )?

Thanks in advance

DEEPAK V