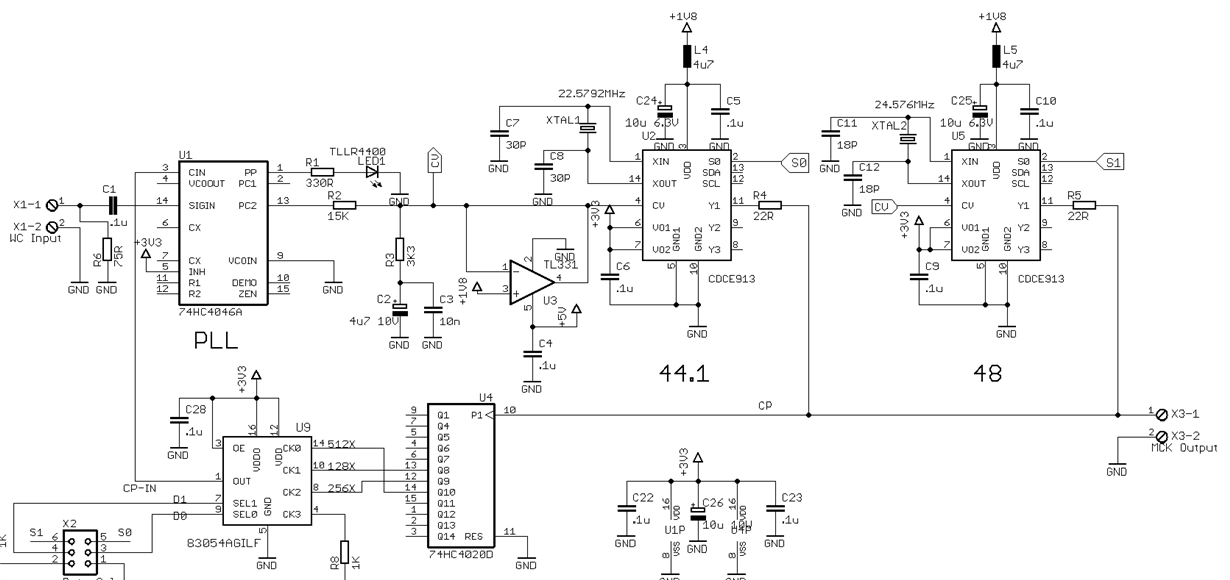

Part Number: CDCE913

Hi folks,

I'm not too expert in PLL's.

I decided to replicate the Audio Clock design on "SCAA088 - Generating Clocks for ADCs from Word Clock", I'm not using the cdce internal registers (I²C) to divide the feedback,

rather a 4020 as a divider. The crystals used are these.

They're rated for ±30ppm freq. tolerance and stability, C0 max. 7pF.

I couldn't find the ones suggested in the App note.

I must point out that I'm using only one 5.6pF correction external capacitor to get exactly the needed 22.5792MHz frequency output.

The problem:

It seems the output of cdce is not in-sync with the Word clock input.

As an example, I took some vid from my scope, the system receives a 44.1kHz Word Clock, and outputs a 512x Fs Master Clock at 22.5792MHz.

Probing:

1. 7046 PC 2 output, pin 13 (Phase Frequency Detector);

2. LPF out - CDCE913 CV input, pin 4

3. SIG IN (yellow trace) and COMP IN (blue) of 7046 at 44.1kHz.

4. SIG IN (yellow trace), 44.1k, and CDCE913 Y1 output (blue) at 22.5792MHz (at sec. 5, I changed the trigger source to Ch2 to show the correct 22.5792MHz count).

I noticed that when there's no signal present at SIG IN, the cdce control voltage is at 0V, while when signal present, the CV is always at it's max of 1.8V .

The 7046 PFD output (see first vid), behaves strangely. Shouldn't it have only small pulses?

Any suggestion greatly appreciated.

Thanks!

The schematic: