Hello,

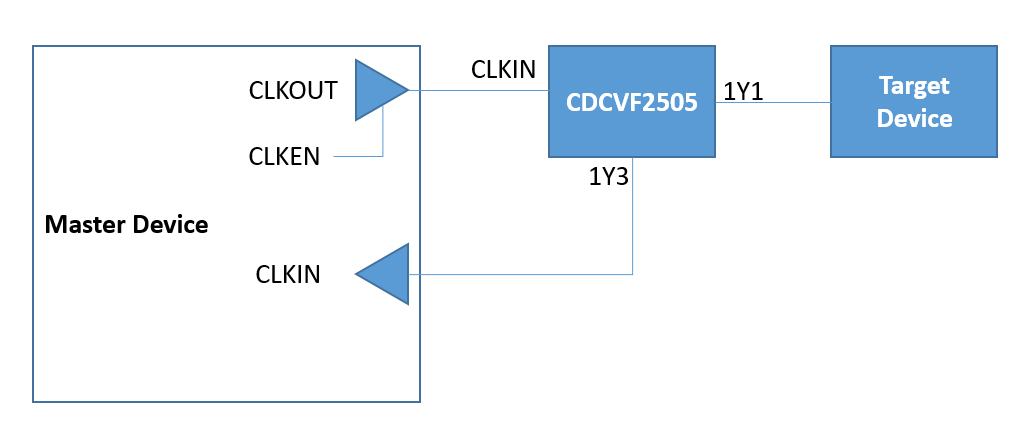

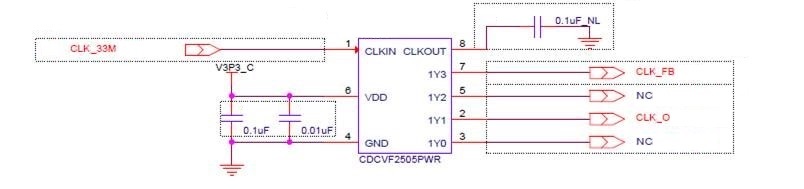

I am working with a board that uses CDCVF2505 for gated clock distribution. The input clock toggles and stops for some period of time for power savings, but we noticed that occasionally the output clock from the buffer does not have a sharp falling edge and instead is decaying slowly. Blue is the input clock and yellow is the output:

Is this a known issue for this device? Are there any recommendations for mitigating it?

Thank you,

ilya