Hi, Team:

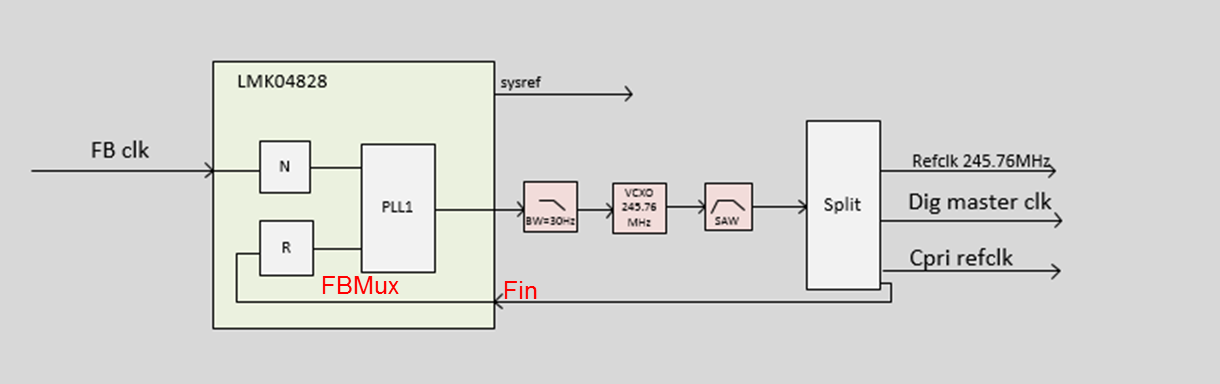

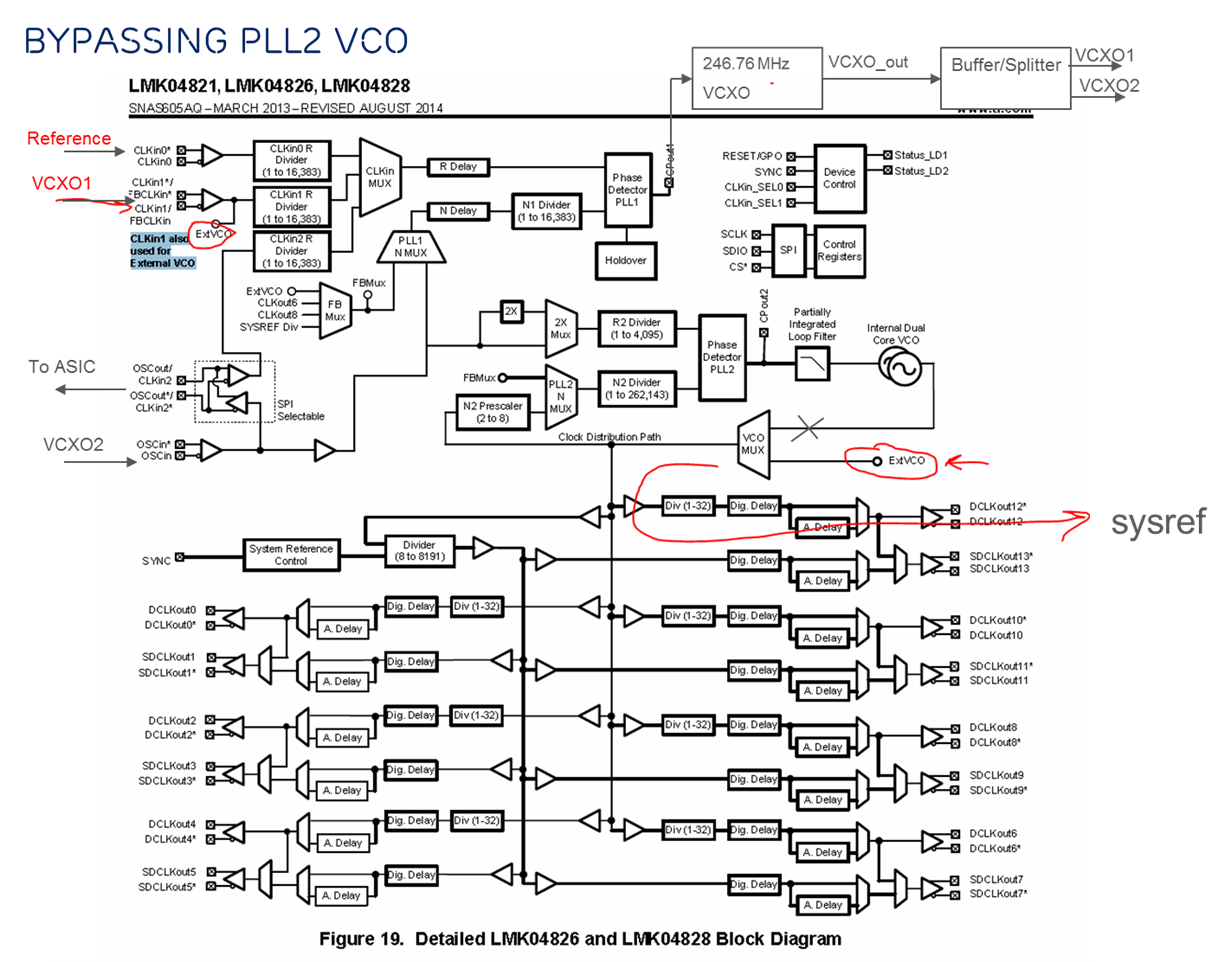

My customer wants to use LMK04828 in bypassing PLL2 and internal VCO mode.

The reference signal is feeded into CLKin0 which is 122.88MHz, external VCXO is connected to Fin or ExtVCO (CLKin1/FBCLKin), FBMux is enabled which routes ExtVCO to PLL1 N divider.

My thinking it should be okay to work, but I would like to get the confirmation and your comments on it. Thank you so much!