Other Parts Discussed in Thread: TMS320C6678,

I use CDCM6208 to generate clock for TMS320C6678. CDCM6208 's input is 25MHz crystal connecting to SEC_REFP/N.

CDCM6208's output is 156.25MHZ for Y0/Y1/Y2,100MHz for Y4/Y5/Y6,Y3 and Y7 are floating. VCO fraquency is 3.125GHz.,the actual output frequency is 90% of what i expect,Y0/Y1/Y2 is about140MHz,Y4/Y5/Y6 is about 90MHz.

I try to change output frequency,I changed Y0/Y1/Y2 to 125MHz,Y4/Y5/Y6 to 100MHz, This time VCO frequency is 3GHz. and the actual output frequency is 94% of what i expect,Y0/Y1/Y2 is about 118MHz,Y4/Y5/Y6 is about 94MHz.

I use osilloscope to observe the output frequency ,the waveform is very stable in spite of the wrong frequency .

I configure statuso pin is PLL_LOCK,status0 pin is NOT PULL UP.

I measure the CDCM6208's power ,and it is 3.35V. I think power is OK.

I use Spartan6 to control the CDCM6208 with SPI, the verilog code I using is OK beacuse I use the same code to control CDCM6208 of other board(called board A) generate clock frequency successfully.

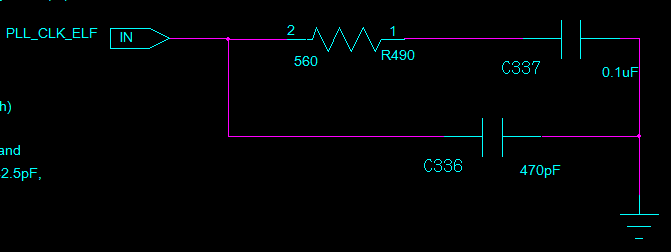

The loop filter is as below and it is same as the board A,

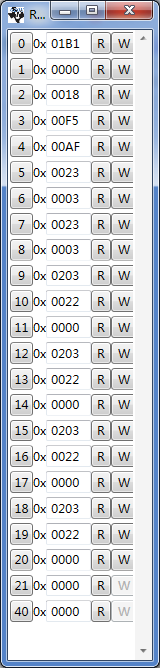

The register of CDCM6208 is as below

The wrong and stable output frequency puzzled me a few days,please help me .