Other Parts Discussed in Thread: 66AK2H12, LMK03328

Hi,

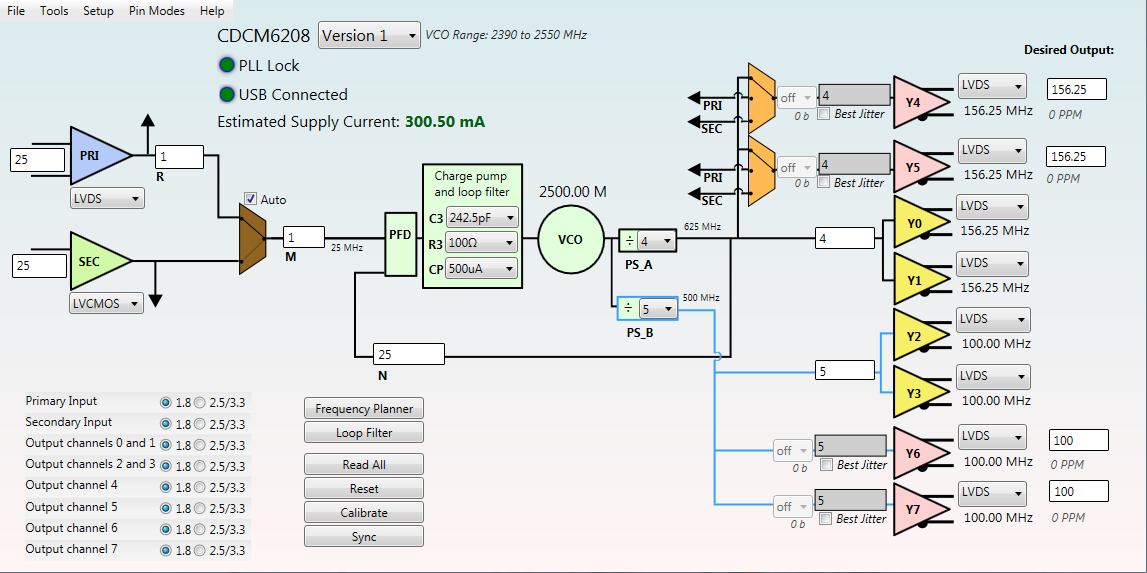

I am planning to use CDCM6208 to clock a K2H soc, using a 25MHz crystal at the SEC_REF pin.

Using the crystal mentioned in CDCM6208 datasheet ( NX3225GA), Please let me know whether is it possible to attain jitter requirements of K2H device?

Thanks & Regards,

Madhu