Other Parts Discussed in Thread: CODELOADER

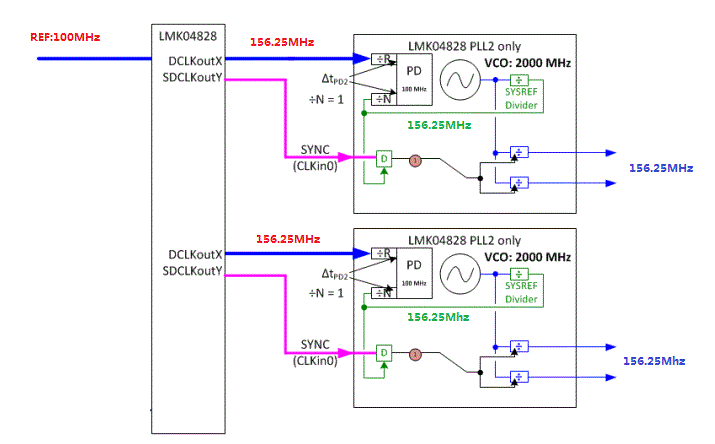

I need 10 pairs of DCLK and SYSREF to serve 10 DAC chips.

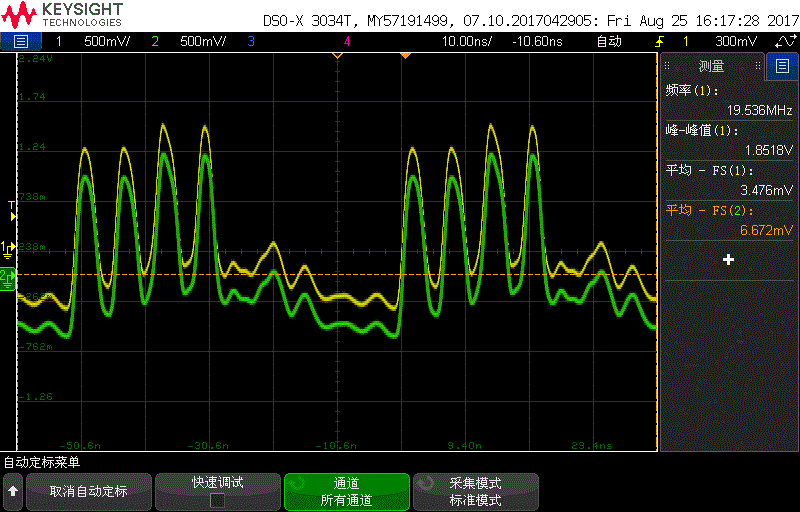

DCLK = 156.25MHz,SYSREF = 19.53125MHz

a LMK04828 can provide 7 pairs of DCLK and SYSREF,so i need two LMK04828 in parallel.

Master Reference input:100MHz,the master LMK04828 provide 156.25MHz DCLK and 19.53125MHz SDCLK(continuous,used for SYNC input for slaves)

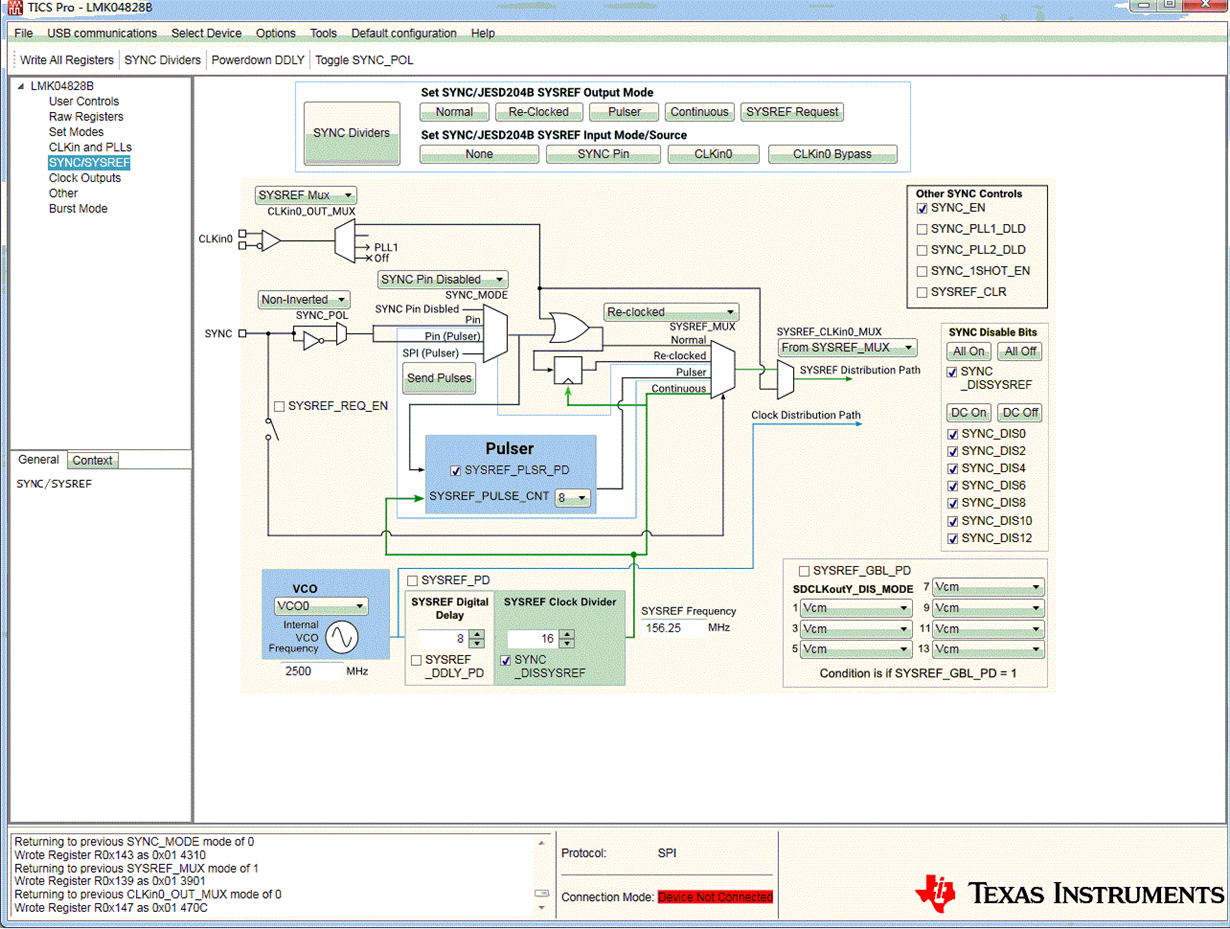

SYNC PIN and CLKIN0 PIN of master LMK are not used

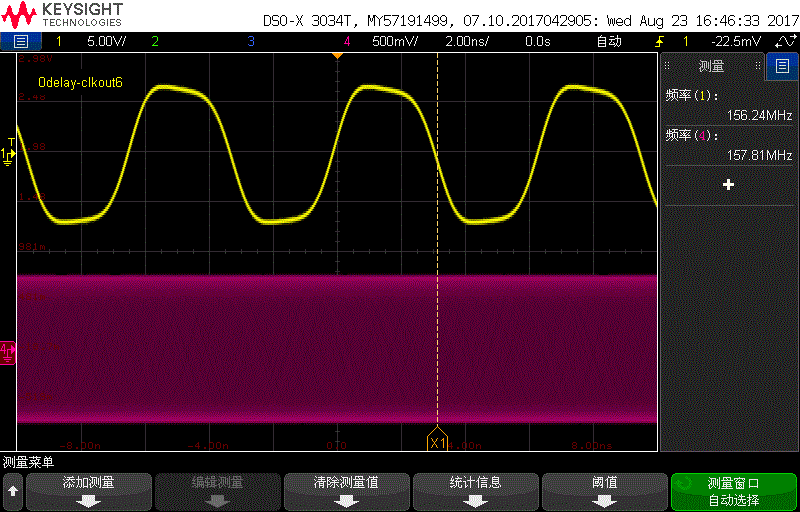

my problem is:DCLK output of two slave LMK are not phase alligned.and no SYSREF output.

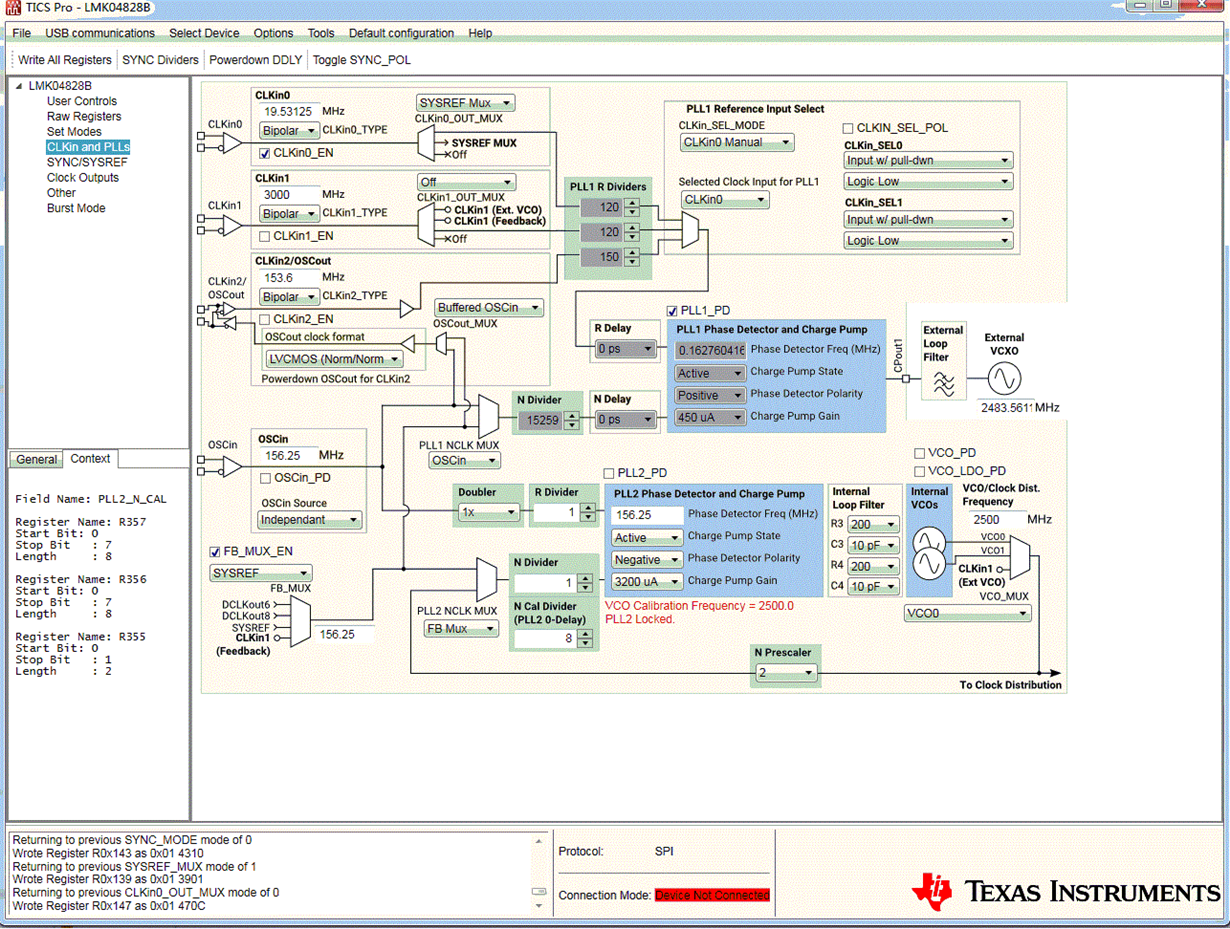

I use the Clock Configuration Tools to export register values,a SPI mater module in FPGA finish LMKs setting.

where did i wrong??