Part Number: LMK04828

Other Parts Discussed in Thread: CODELOADER

two slave LMK(LMK_A and LMK_B) are in single loop SYSREF 0-delay mode, the SDCLKouts should be phase aligned with reference input after power-up,with a SYNC pulse,all the DCLKs and SDCLKs should be SYNCed.

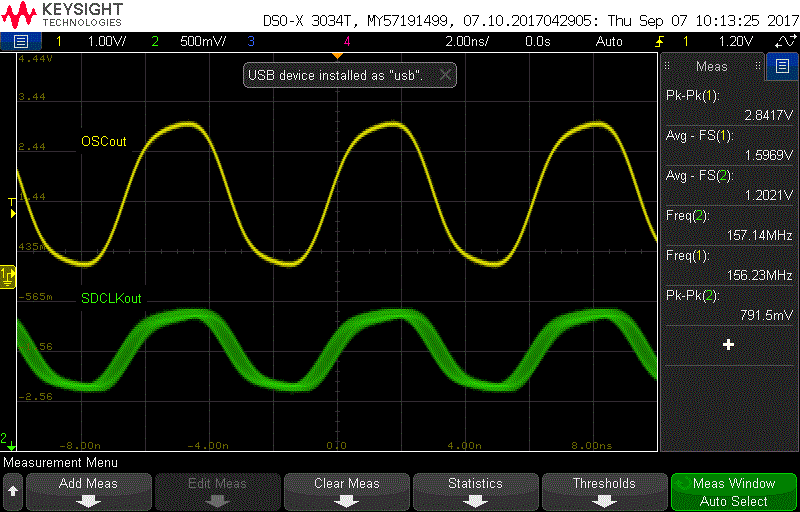

now i can see the OSCout of two slave LMK are phase aligned and stable,SDCLKout of slave LMK_B are phase aligned with OSCout too,those are what expected,

But OSCout_A are not phase aligned with SDCLKout of LMK_A?

the lock indicator LED is ON,and two slave LMKs are just the same, can this be a phase detector error?? or the chip is damaged ??

and SYNC_DISSYSREF bit must be enabled in SYSREF 0-delay mode,am i wright?

even though SYNC PIN Disabled,SYNC_DISSYSREF enabled,toggling SYNC PIN can still reset phase of SDCLKs,why??

Thanks