Other Parts Discussed in Thread: LMK00304, LMK01000,

Hi, I am having hard time about choosing a right topology for my design .

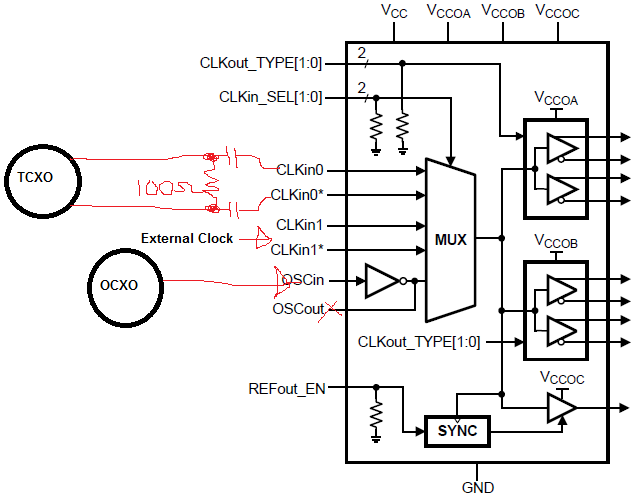

I have three reference clock which I want to choose one at a time for my PLL's(LMX2594) reference clock.

- One clock reference is OCXO on my PCB for low phase noise

- One clock reference is TCXO on my PCB

- And the other is external clock.

The problem is TCXOs can't drive 50ohm loads,(at least the ones I have searched. Could you please suggest me a one if you know). So I started searching fanout-buffers. However, they require high slew rates like LMK00304 and my OCXO's and TCXO's output slew rate is about 3V/5ns.

Could you please suggest me a solution for this problem ? What is the best buffer with lowest additive jitter and requires lower input slew rates ? Or is there a better solution than using fanout buffers? LMK01000 is the best one I could find .

Also I couldn't find any information about minimum required slew rate of LMX2594 reference clock.