Other Parts Discussed in Thread: TLC555,

Continuation of troubleshooting from this post: https://e2e.ti.com/support/clocks/f/48/t/650131. The problem in that post was solved with the reduction of output capacitance to remove chip heating.

The duty cycle of the 555 timer's output is changing based on the output load. With approximately 72.5ohms (measured), the duty cycle is at 100%. With 120ohms the duty cycle decreases to ~80%. I am concerned the 555 timer has sustained damage from previous troubleshooting and operation, but am looking for any other explanation as to why the loading can affect the duty cycle of the chip, short of damage.

Having probed the Trigger and Threshold pins, the voltage at those pins is not rising beyond ~6V, and the control voltage is at ~6.5V -> so the voltage thresholds are okay, but the trigger/threshold is not charging up beyond the 6.6V needed to trip the trigger.

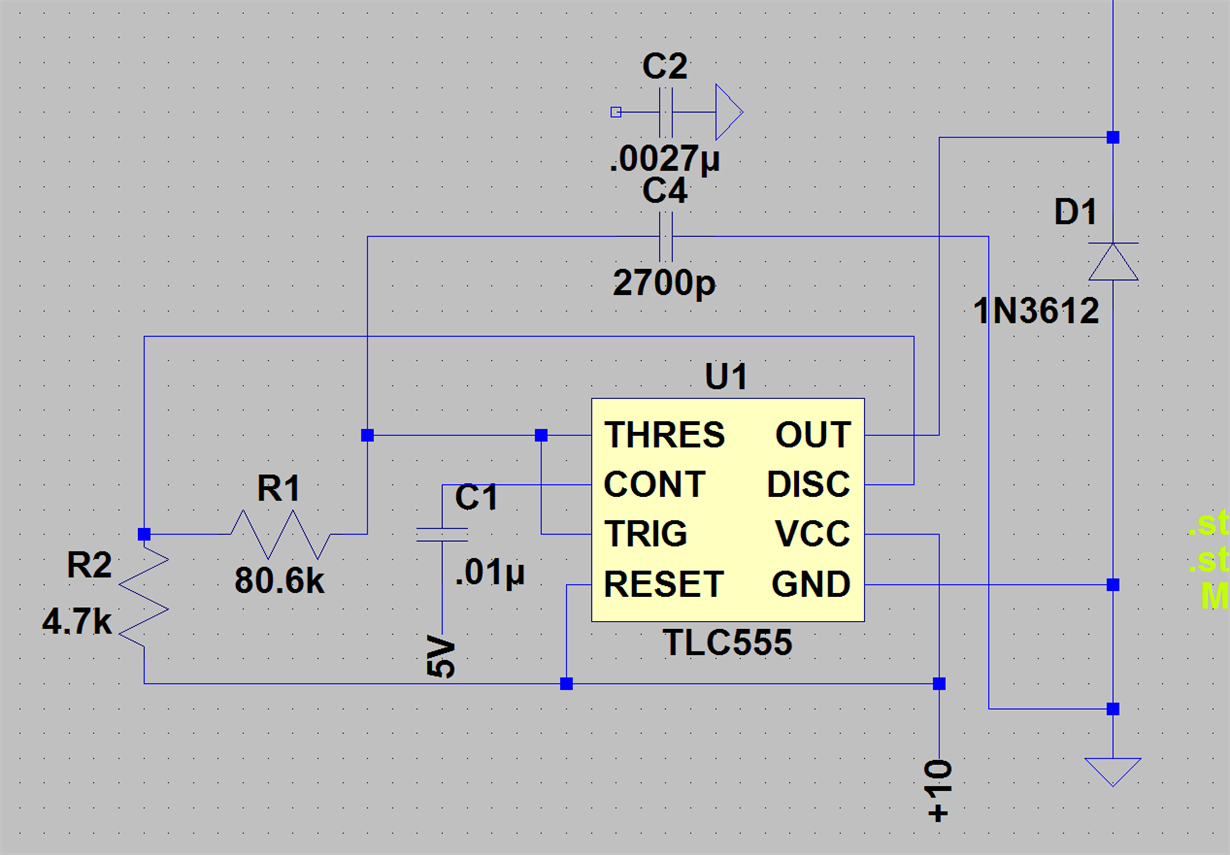

I apologize for the LTSpice schematic, but I am still learning TI-Tina and this was faster for me right now. Simulation does not show a problem or frequency shift with different loads, though admittedly the only simulation chip available is the TLC555, not the LM555.

I am continuing to troubleshoot the problem in the lab, and will try a chip swap to see if the operation changes.