Other Parts Discussed in Thread: LMK04616

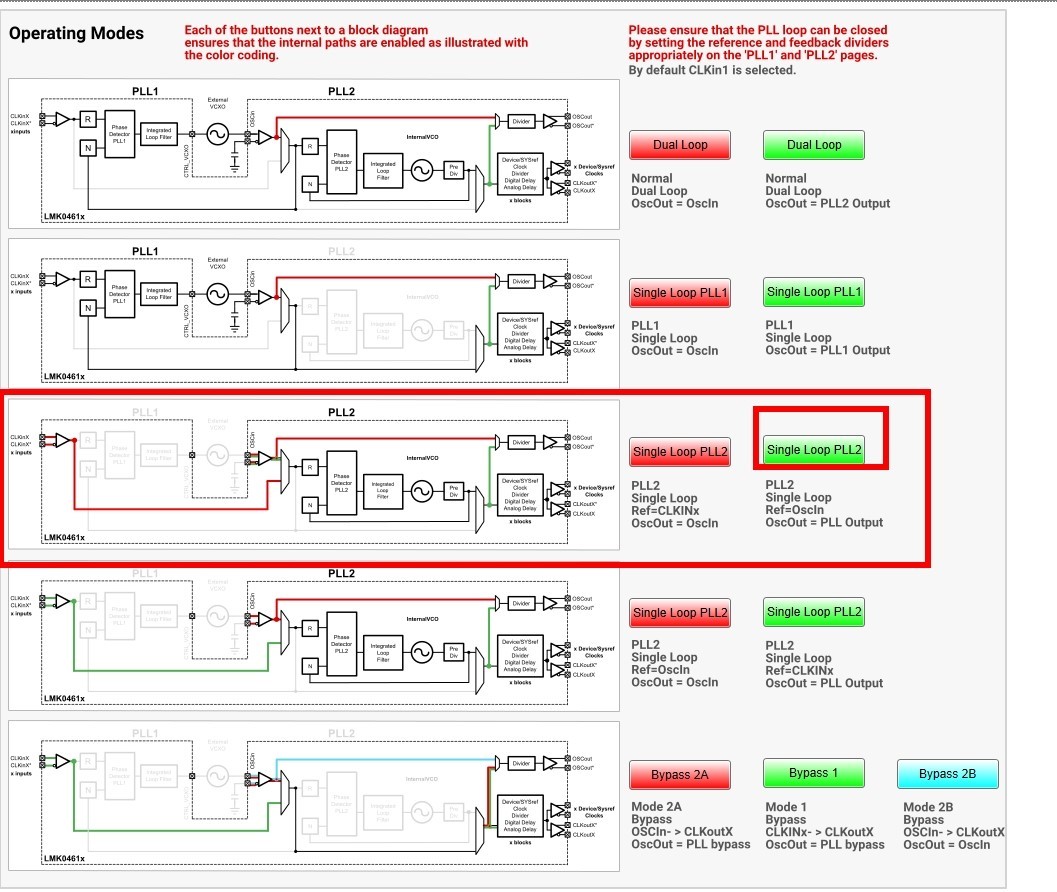

Our clock board is now ready to use the LMK04616 chip. We want to be able to use zeros delay mode.

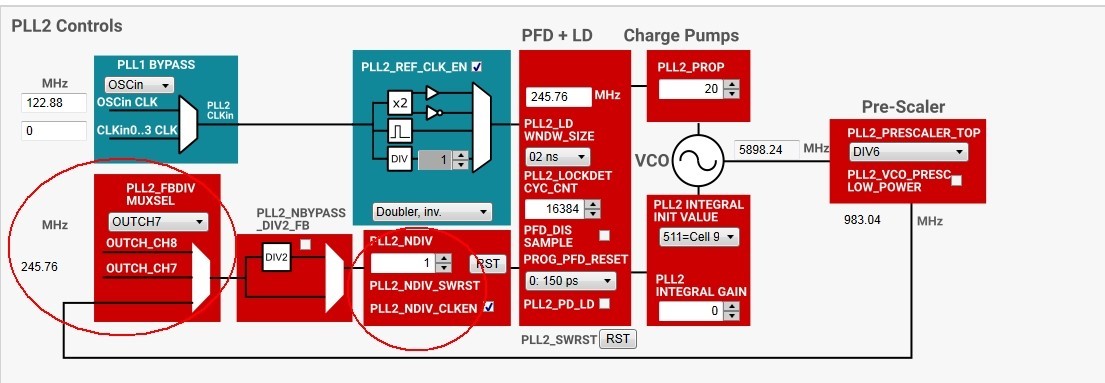

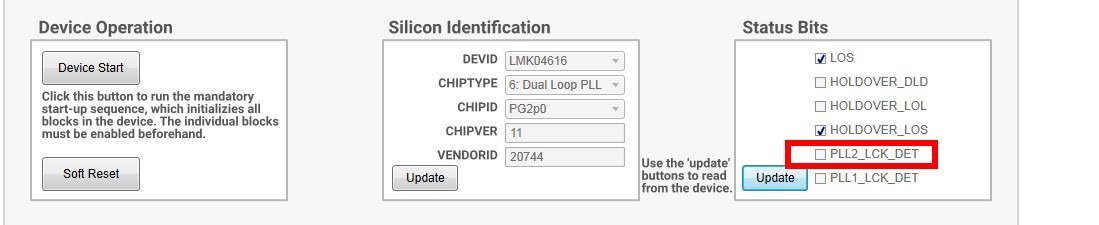

According to the document register 0x146, select the OUTCH8 output for feedback, and then the corresponding N to modify the PLL2. But when the configuration is explained by the register in the document, PLL2 is not locked.