Hi All

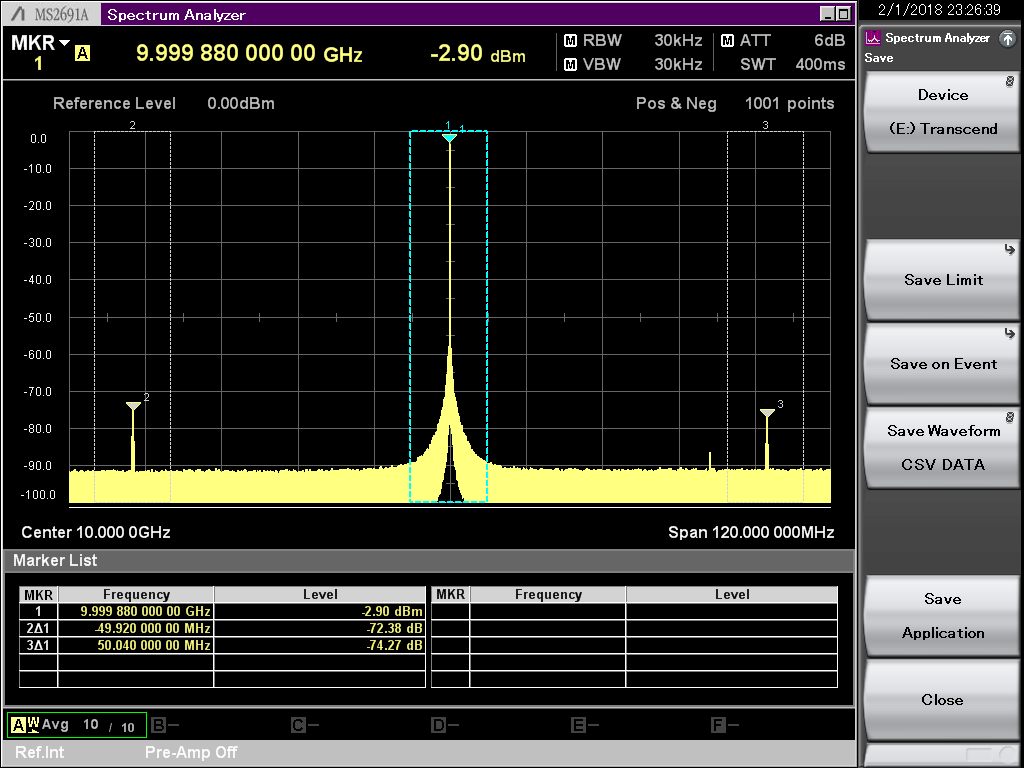

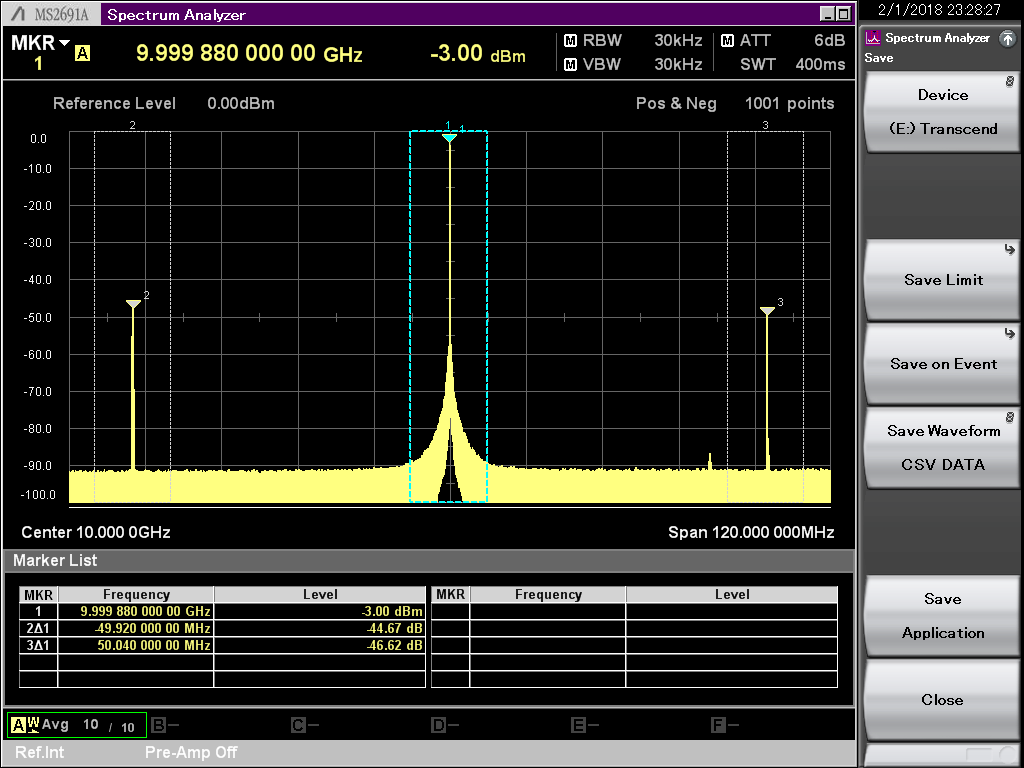

I ran into an issue I don't completely understand and I also didn't find any further information about that. I'm feeding a 100 MHz Ref CLK to the PLL and divide it by 2 in the input path to get a PFD of 50 MHz. Afterwards, I operate the PLL output (A or B, doesn't matter) at, say 10GHz, so there's no output divider enabled. At a Distance of PFD, there are two strong spurs visible in the spectrum analyzer, that are only 50-60dBc down. After consulting the PLLatinum Sim, it tells me that this spur is due to the PFD-VCO crosstalk! Can someone explain me this type of spurs or point me to further reading? Also, is there a way to reduce those spurs?

Thanks and best regards

Fabian