This issue occurs whether using Fast FSK (writing reg 33) mode or writing all 23 bits of the numerator directly (reg 17-18).

Issue details:

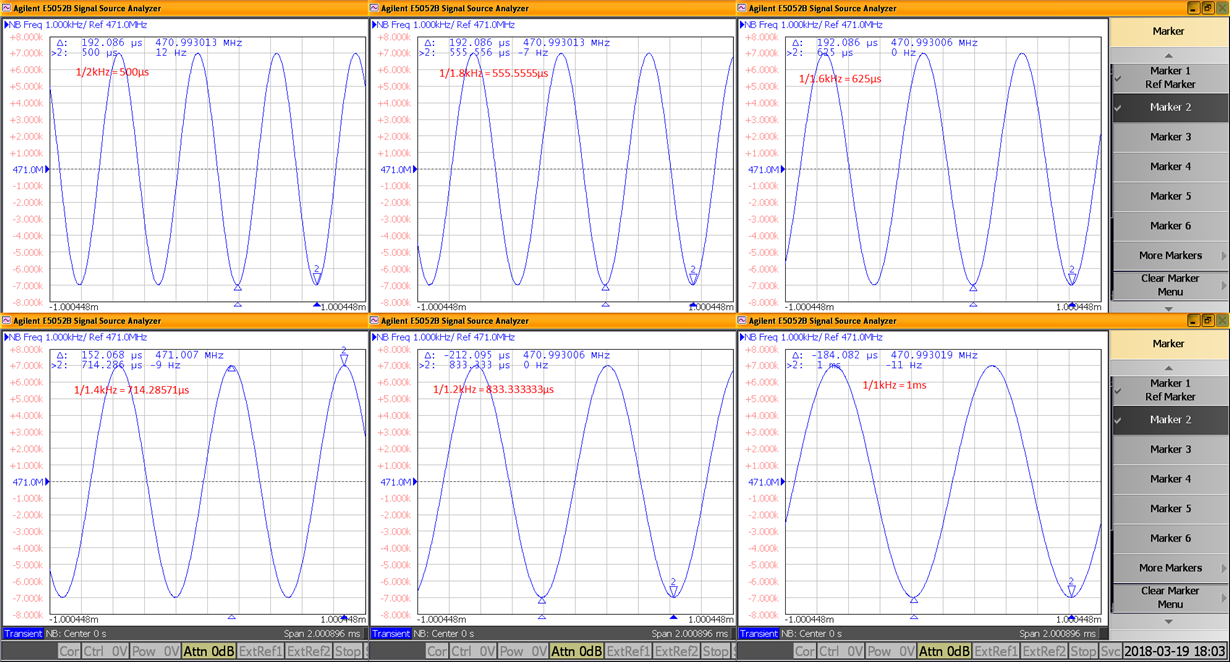

1 - Writing a clean digitally generated sine wave to reg 33 at a 16Khz rate with 7k max deviation produces a clean 7k deviation signal for sine waves up to 1.5kHz -- from 1.5kHz to 2.2kHz, the deviation on receiver shows the LM2571 starts to over-deviate with a peak over-deviation at 2kHz sine wave input -- demod shows 7.6-7.8kHz deviation.

2 - Writing static values to reg33 works perfectly fine and moves the carrier properly based on that static value written.

3 - This issue is apparent on all center frequencies tested.

4 - We are using F2, and I have tried changing charge pump currents and gain (R41, R40); as well as R value of 4th pole, 3rd pole internal loop filter and PFD_delay_F2 (R23, R22); as well as the order of the Delta Sigma Modulator (R20); no changes had an effect (changed values singularly to both extremes and a mid point).

5 - Issue is apparent but much less magnitude at 5kHz deviation -- issue results in 5.15kHz deviation at demod.

6 - Issue is not apparent at 2.5kHz deviation.

Any further insight or direction is greatly appreciated!

Joe