Part Number: CDC3RL02

Hi,

I designed my clock circuit using CDC3RL02, I have a question about MCLK_IN of this buffer.

Does the buffer accept an AC-coupled clock signal as input for MCLK_IN? (The input signal into MCLK_IN in my design is as AC-coupled sinusoid signal from OCXO)

It is specified the specification of MCLK_IN on page 6 the datasheet as below. I think this means that input signal into MCLK_IN should be DC-biased signal.

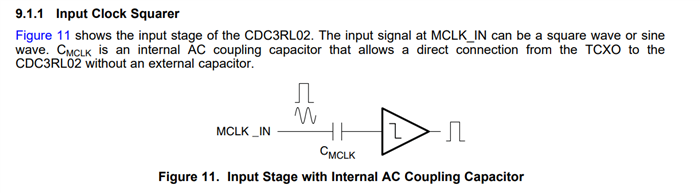

But, on page 11 of the datasheet, there is an AC-coupling capacitor inside the MCLK_IN input as below. I think this means that an AC-coupled signal is also acceptable. So, I am confused. Is it possible to be applied AC-coupled sinusoidal clock into MCLK_IN?

I would appreciate your advice.

Thanks.