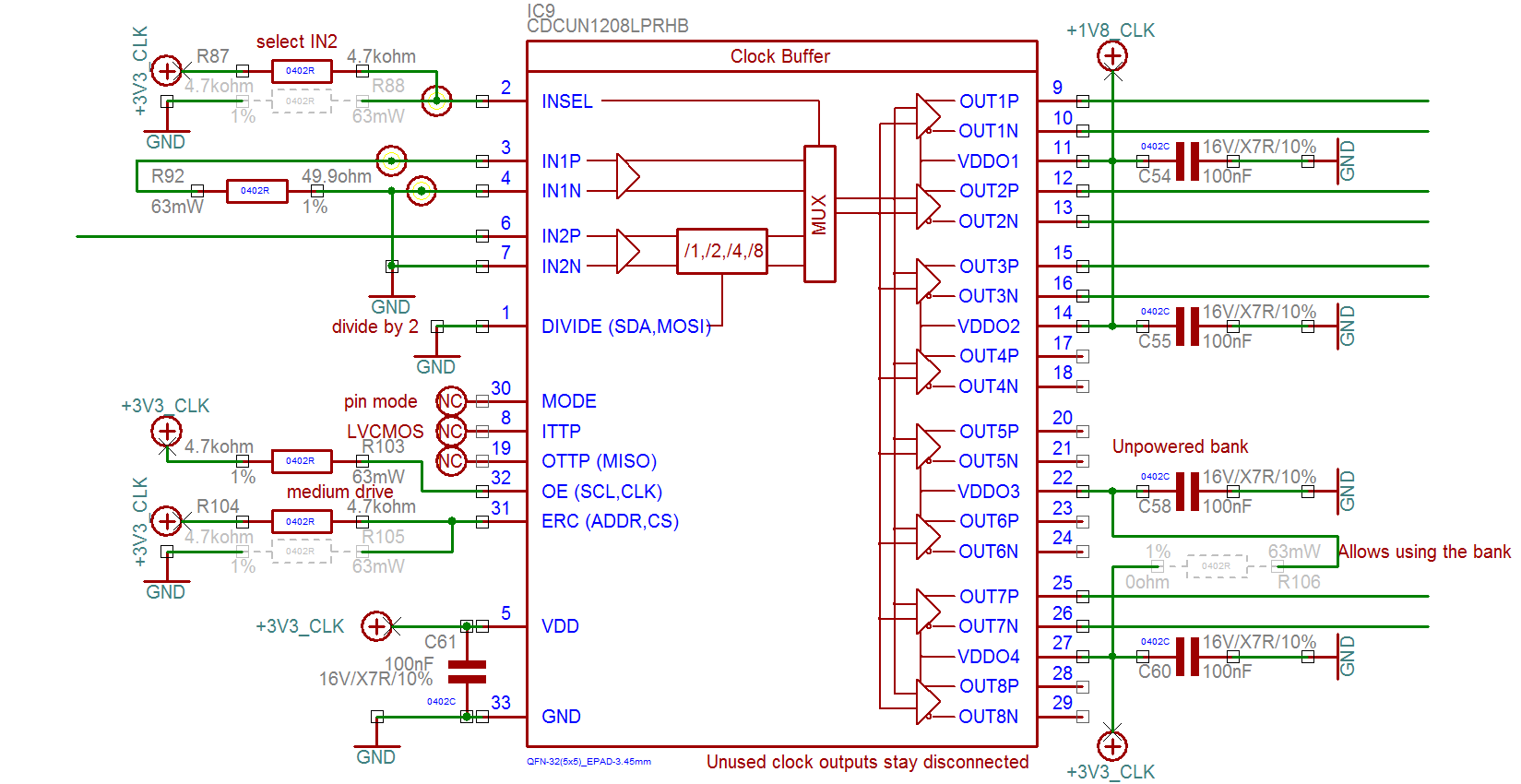

Part Number: CDCUN1208LP

I have an issue with the CDCUN1208LP when trying to power up. The configuration is as follows:

- 3.3V powers the core (pin5) and VDDO4 (pin27)

- 1.8V powers VDDO1 (pin11) and VDDO2 (pin14)

- VDDO3 (pin22) is floating with a 100nF cap to GND

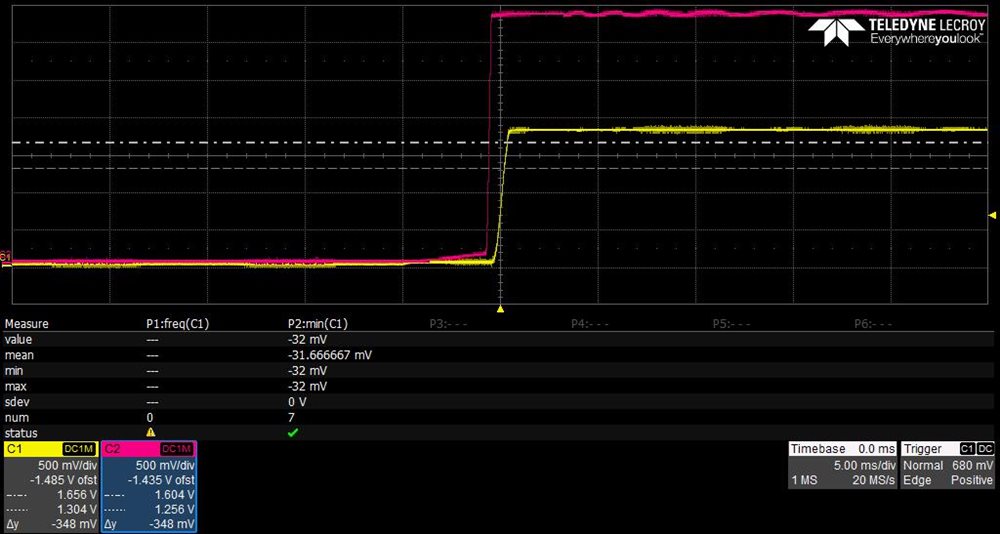

With the following sequence the CDCUN1208LP starts up and seems to work correctly - note the bump in the 3.3V before actual turn on.

I cleared this bump (no other changes are made to the board) and with the following (nicer looking) sequence the CDCUN1208LP does not start anymore!

I think I respect all the power up requirements of the chip, i.e. >6.5V/ms rise time and core (3.3V) before or at the same time as VDDOx voltages (3.3V and 1.8V)