Other Parts Discussed in Thread: LP2985, CODELOADER, LMX2541, , LMX2531

Dear Sir, Good Morning.

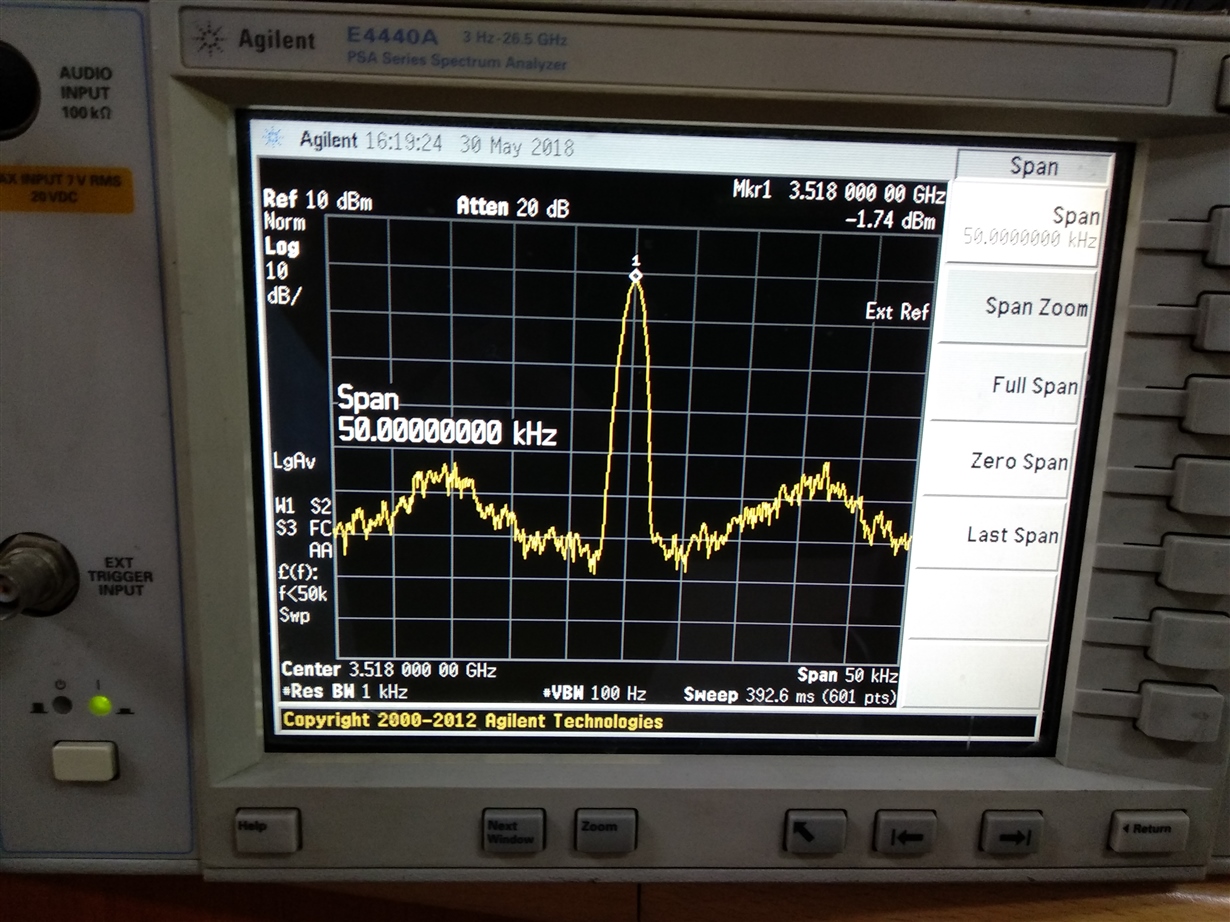

I am facing problems locking issues with LMX 2581. I want to use it as a synthesizer for generating multiple freq. (one at a time) 950 MHz, 990 MHz, 1030 MHz, 1070 MHz & 1110 MHz using 20 MHz Oscillator input. The RF output setting of 950 MHz freq. comes 948.62 MHz that is also not locked . I have used the the 3 LDO for supply of LMX 2581 (LP2985) and presently for testing i am giving 20 MHz from signal generator around +3 dBm at Oscillator input. The phase noise performance is also very bad. I have checked the circuit as per your evaluation Board. please help