Hello,

When we design PLL parameter for communication equipment, what parameter should we care about?

We are struggled LMX2592 design. The error rate doesn't reach the target.

I would like to know what parameter should be pay attention in general for error rate.

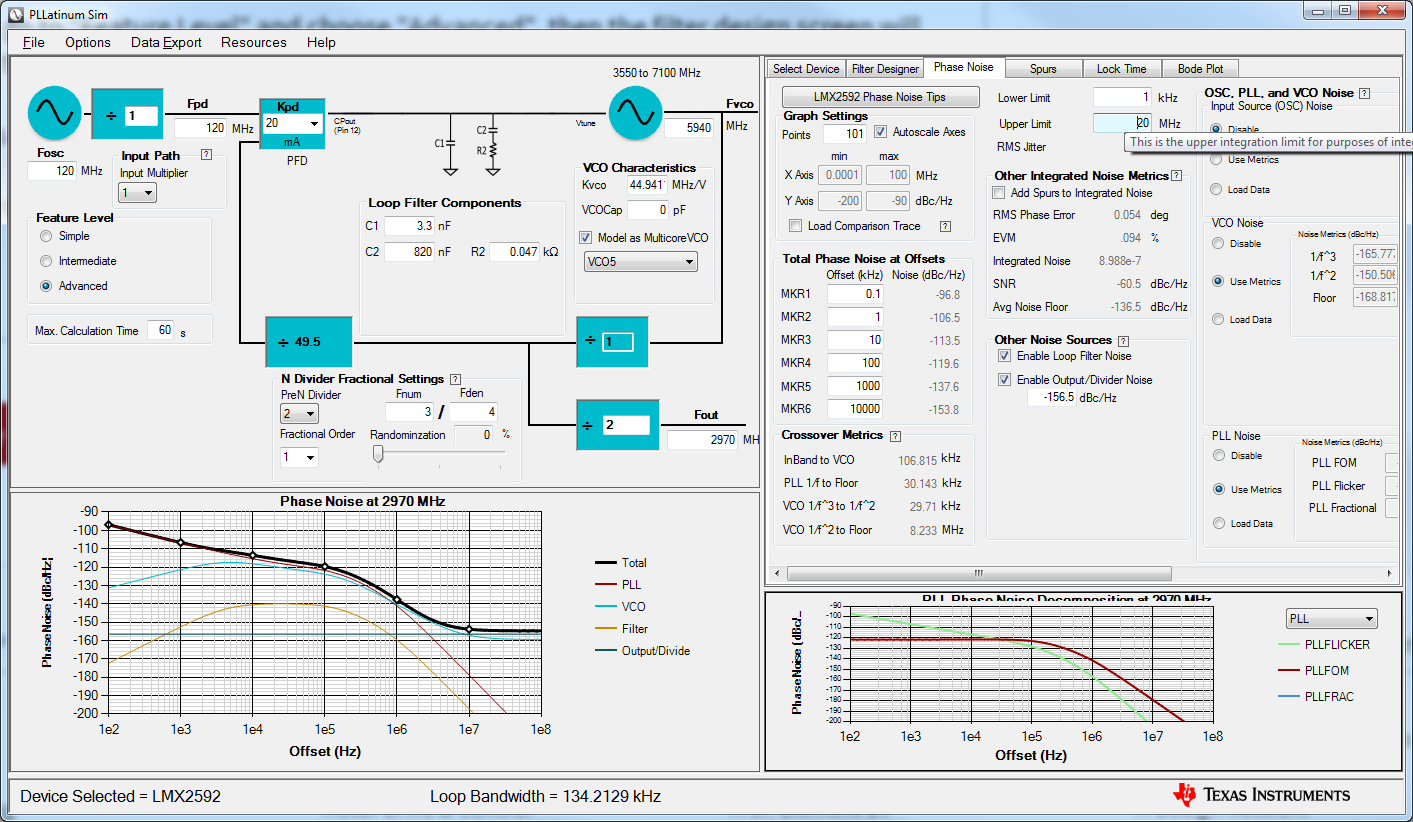

And also make the parameter of PLLatinum Sim.

The condition is below.

1) Reference clock is 120MHz.

2) Output frequency is 5940MHz.

3) VCO frequency is 5940MHz.

We would like to try the parameter then narrow down what parameter should be changed for improvement.

Best regards,

Toshihiro Watanabe