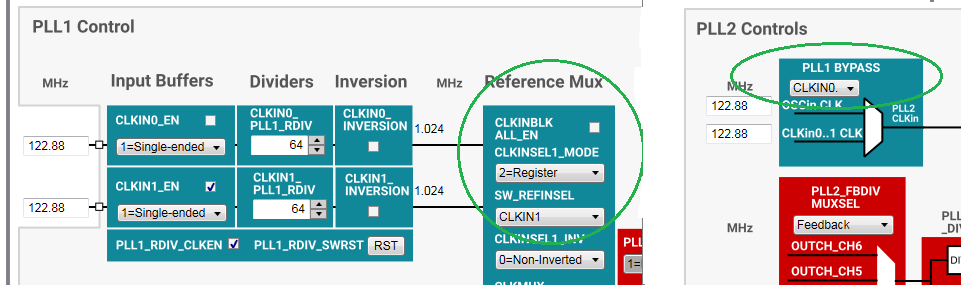

Below are LMK04610 registers I used to generate clock with OSCIN as PLL2 reference clock and bypass PLL1.

But when I change reference clock of PLL2 from OSCIN to CLKIN1, PLL2 can not be locked.

00101E

001640

001900

001A31

002Aff

002C88

002E0e

002F01

00311C

003463

003603

003863

003A02

003C62

003E62

004063

004203

004402

004628

004802

005004

005208

006C00

006D28

006E1b

007214

007404

007601

007701

00800A

008601

00921C

009380

009502

009610

009760

00B001

01463C

015114

01520F

001101