Hi,

We are planning to use your Low Jitter clock buffer CDCLVC1310 to distribute our LVCMOS SiT5356 TCXO oscillator (datasheet link given below) output clock to multiple units by using coaxial cable.

www.sitime.com/.../SiT5356

In this our major requirement are given below,

No.of clock output : 7 (Min)

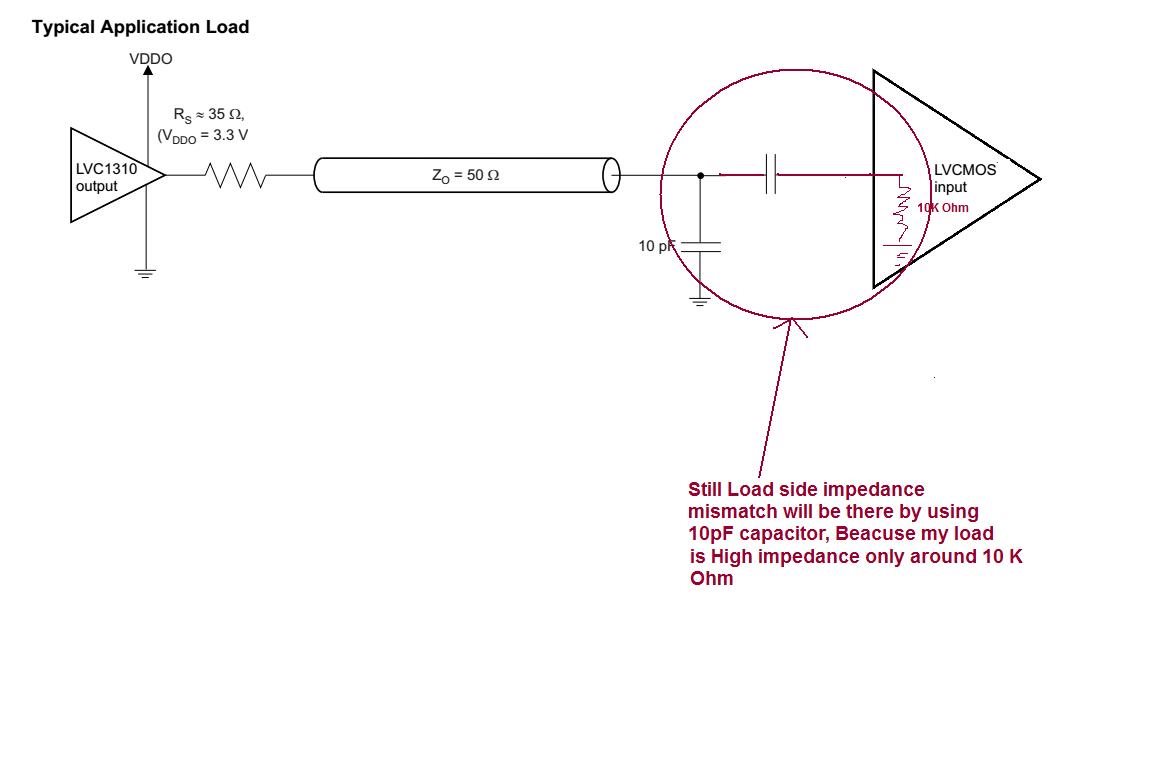

Output drive : 50 Ohm coaxial cable to another units

Phase noise degradation : Very minimum

Please find our LVCMOS oscillator phase noise at 30MHz output (which is input to clock buffer) for your reference.

1 Hz offset -70 dBc/Hz

10 Hz offset -98 dBc/Hz

100 Hz offset -117 dBc/Hz

1 kHz offset -138 dBc/Hz

10 kHz offset -144 dBc/Hz

100 kHz offset -144 dBc/Hz

1 MHz offset -157 dBc/Hz

5 MHz offset -158 dBc/Hz

Will it meet our above requirement or do you have any other better part for our application requirement?

Also suggest if you have any application circuit for 50 Ohm load support.

Regards,

Sugumar K