Other Parts Discussed in Thread: LMX2592, TIDA-01410

TI E2E Clock Forum,

I previously had a productive dialog with Dean about our requirement to generate a 600MHz clock from a 1200MHz differential input source derived from a DDR4-based DIMM’s LVCMOS clock. We were successful when inputting our 1200MHz clock into the OSC inputs of the LMX2594 EVM demo platform. However, now we are attempting to generate the 600MHz clock on our hardware platform and are not seeing the same results.

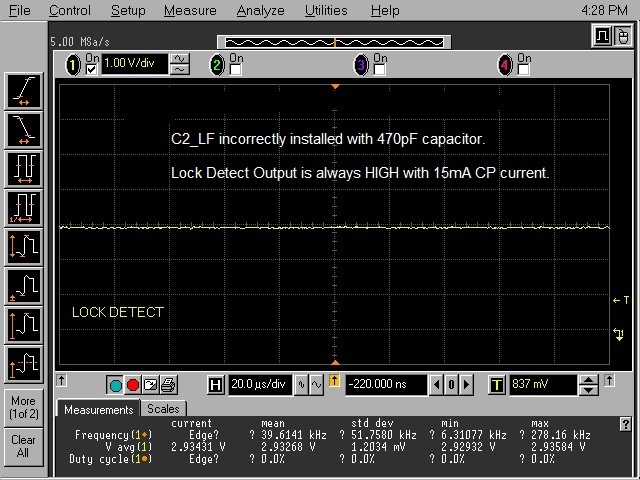

We have a very clean and monotonic 1200MHz differential input clock with ~ 2V P/P swing. We are getting a very clean output clock from the LMX2594 with the 1.2V P/P swing we need delivered to the differential 100 ohm load at the destination FPGA input with the RF output strength set to 15. Our 12GHz oscilloscope shows the output frequency to be very close to the 600MHz we require, but apparently not close enough as we cannot get the input and output clocks to sync on the scope shots as we did with the demo board bench setup in order to confirm deterministic phase lock. I suspected that the loop filter might be the problem so I tried all the charge pump gain settings in TICsPro while monitoring the lock detect signal. The only setting that gave us a constant lock indication was the 12mA setting. The other settings resulted in either no lock or intermittent lock. I realize that even a steady lock detect output is a ballpark indication at best. So we’re apparently close but not close enough.

Our hardware design is based on the reference design in the LMX2592 EVM User’s Manual. We have been very liberal with bypass and bulk capacitors on the 3.3V rails and LDO outputs. The output circuit uses the 50 ohm scheme as recommended in the data sheet including the 18nH choke on the output driver power rail. The loop filter is similar to the TI design with the exception that due to space restrictions, we used 0201 components rather than the 0603 parts indicated in the BOM. The discretes in the loop filter are closely grouped on the pin 35 side of the LMX2594 with C4_LF placed as close to pin 35 as possible per the datasheet layout recommendations. This is different than the demo board which has the loop filter discretes grouped on the pin 12 side of the LMX2594 on the demo board. I hope this is not a deal-breaker. We are using a 16-layer PCB with all the loop filter interconnects except the pin 12 connection on layer 1 with a full ground plane on layer 2. The pin 12 connection to the loop filter connects to the filter discretes using vias between layer 1 and layer 3. The OSC inputs are terminated with a 100 ohm resistor followed by two 0.1 uF AC coupling capacitors as in the reference design. We are using the EVM control module and TICsPro with the 10-pin connector to program the LMX2594. The following lines in the 10-pin interface are used: SDI, SCK, CSB, MuxOut, GND. The remaining pins are NO_CONNECT.

When we get our “lock” indication, the LMX2594 is programmed as follows:

Freq = 1200 MHz, Doubler = X1, PreR = 24, R = 1, Fpd = 50 MHz, Charge Pump Gain = 12mA, Included Divide = 4, N Divider = 48, Channel Divider = 16, RFoutA = 600MHz and VCO = 9600 MHz. VCO_PHASE_SYNC box is checked.

Your feedback and guidance in helping us debug this circuit will be most appreciated. I also noticed that there is a 10 August 2018 update on TICsPro which I hope to download and try tomorrow.

Thanks,

Ken