Part Number: LMK04131

Other Parts Discussed in Thread: LMK04133

Hi

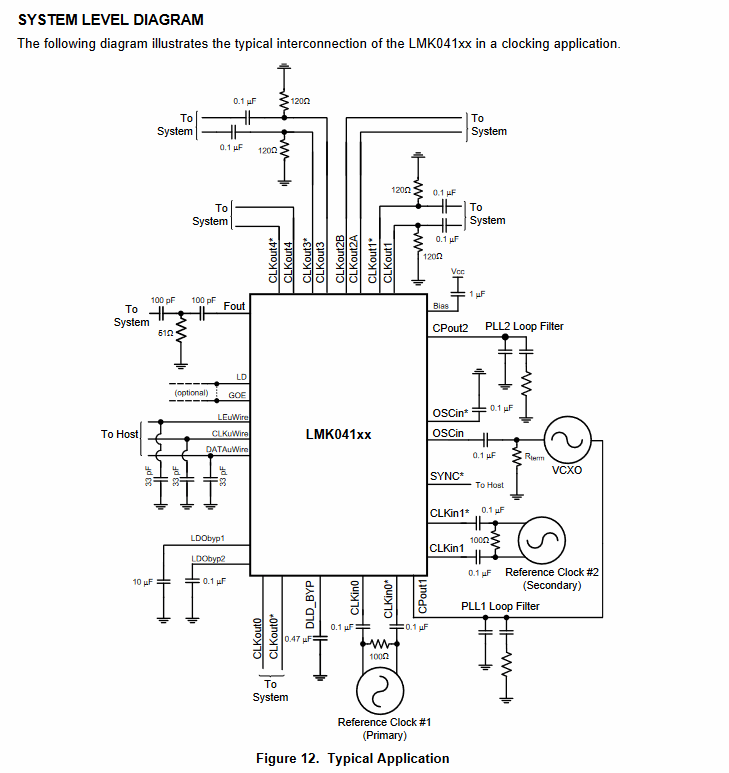

I have a question regarding the clock inputs to the lmk04131.

I do not know how to choose the values of the VCXO connected to the OSCin and the VCO connected to the reference clock CLKin0/1

I need 160 MHz and 320 MHz output. I would like to know how to determine the input frequencies.

Regards Michelle