Part Number: LMK03328

Hello

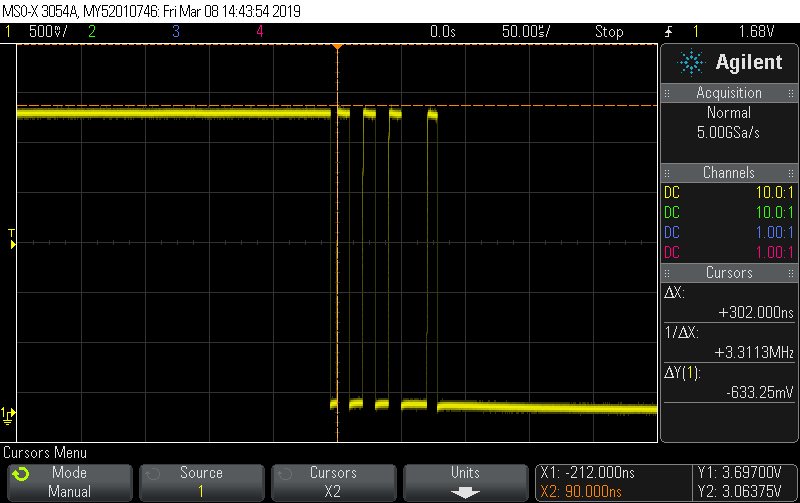

I have connected the digital inputs of the LMK03328 to 1.8V LVCMOS logic as the minimum input voltage requirements are 1.2V/1.4V, however I am having trouble connecting to the board via I2C or toggling the SYNCN pin. Is it possible that the 1.8V logic is causing an issue? Thank you in advance.

Regards