Other Parts Discussed in Thread: LMK04828

Hi team,

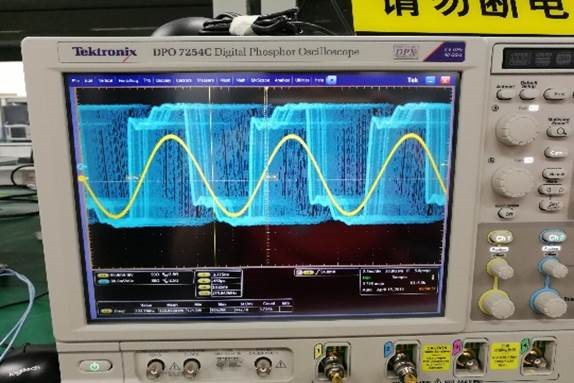

Customer want to achieve fast lock when there is a input. From the spectrum analyzer below, when LMK04610 is locked in 122.88 MHz LMK04610 output clock 122.88 MHz, the phase of the REF CLK clock relative to PLL1 is still changing, and it takes about 5 seconds to be relatively stable.

1. Can I use PLL fast lock function in this application?

2. Why we need 5 seconds to lock compared to LMK04828

3. When I increase lockdec cyc-cnt, the lock time decrease, can I use this?

4 Figure 2 is the best case I tried to get lowest phase shift, any way to improve it?

Thanks.