Other Parts Discussed in Thread: CDCM6208, CDCM6208V1EVM

Hi all , I have a question about CDCM6208.I have a development board with CDCM6208.I configurate the CDCM6208 with SPI mode but it can't work and PLL of it isn't locked.Why for it?

The Phenomenon of it is followed :

1.SPI is normal because I can write register and read the correct value of it.

2.I set register3 0x10F0 while the pin of status1 is high and status0 is low.

3. I measure the voltage of ELF pin and the voltage is almost zero (0.015V).

4.The output pins of CDCM6208 have no clock.

The follow picture is schematic of my board:

PS: the power supply of CDCM6208 is VDD_PLL1(3.3V),VDD_PLL2(3.3V),CDCM_DVDD(2.5V)

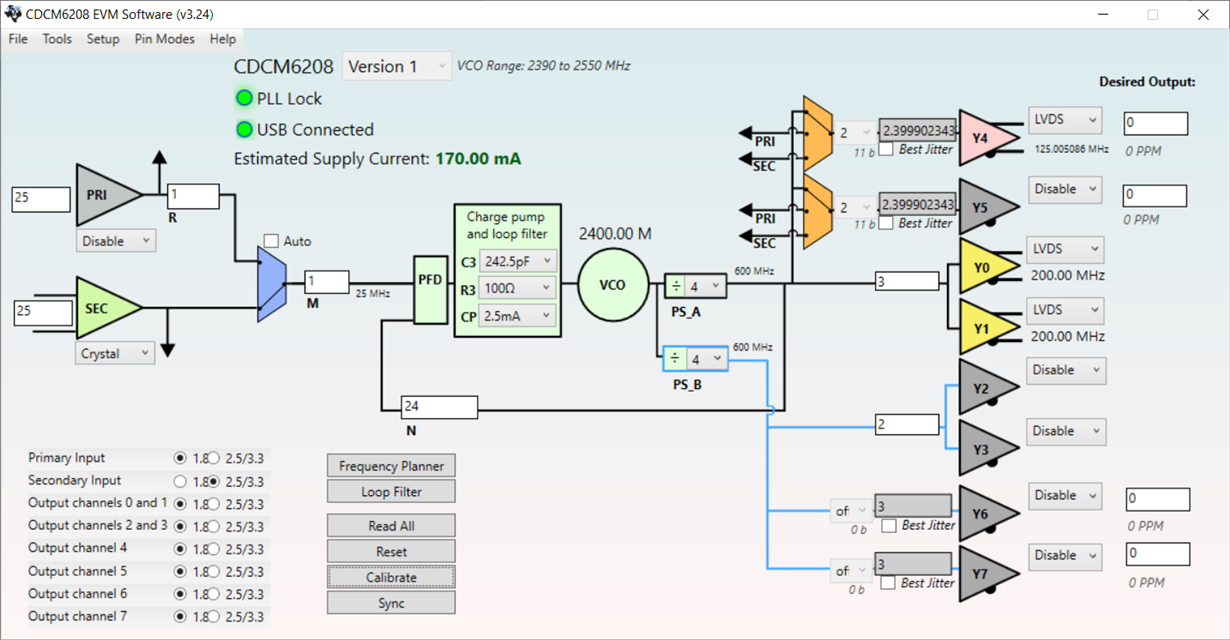

The following picture is my SPI configuration:

I also have an extra question:

1. Whether the power supply of VDD_SEC_REF must be equal with VDD_VCO?

I hope to get a reply soon. Thanks!