Hi Team,

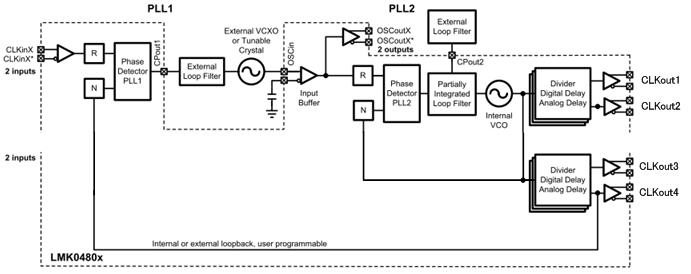

In the LMK04208 datasheet, there is below description for external VCO mode.

I couldn't understand why there would be deterministic phase difference between clock input and VCO feedback clock in 0-delay mode.

Could you elaborate for this description ?

As long as used in 0-delay mode, connecting the clock output to the PFD, I think both phase are synchronized.

Best Regards,

Kawai