Other Parts Discussed in Thread: ADS54J40

Hello.

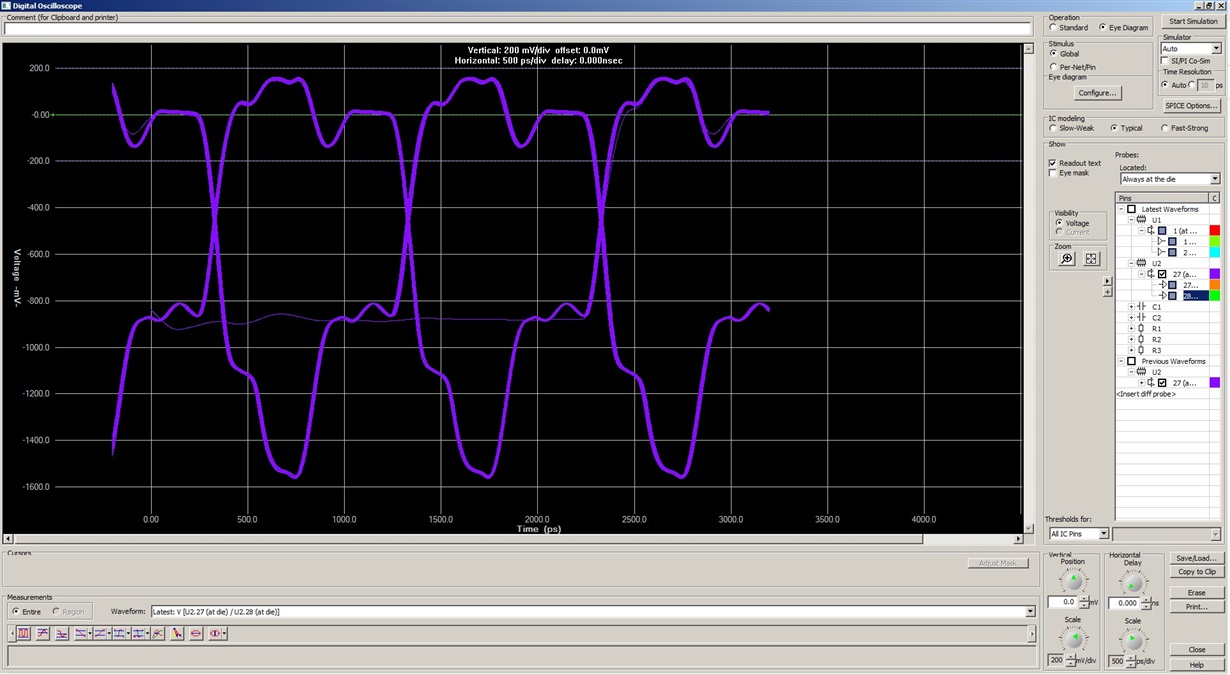

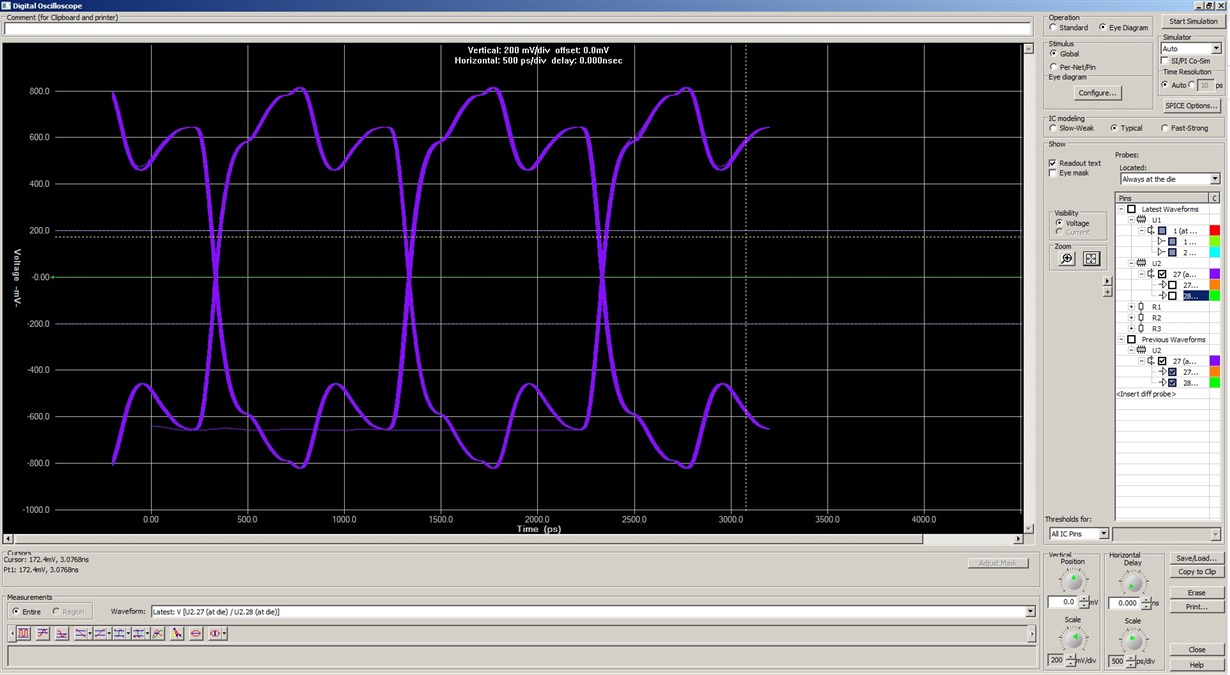

I simulate LVPECL output LMK04828 for ADS54J40 in Hyperlynx, and get a bad result, when termination includes capacitors. Without them, the signal is normal.

termination with capacitors.

without capacitors

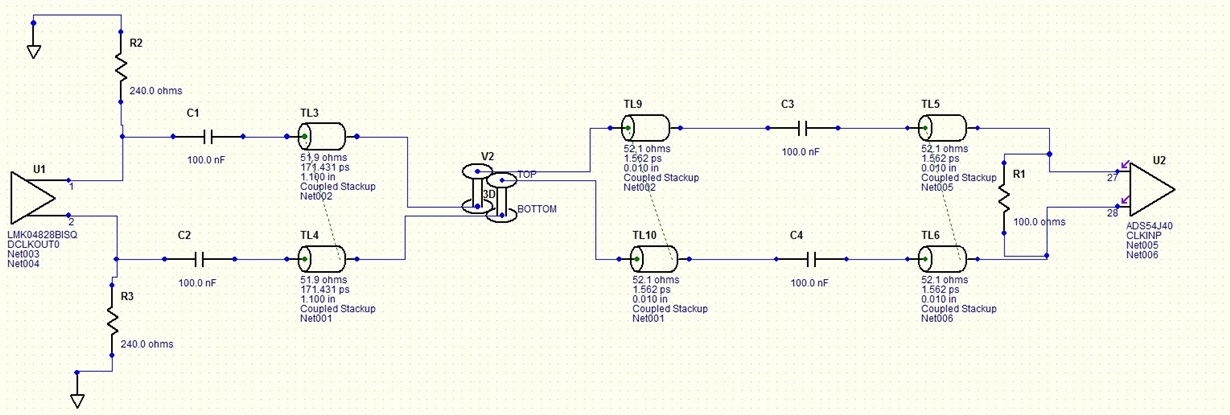

Also, I met different termination options:

with capacitors near LMK and near ADC, or only near LMK. 100 Ohm resistors before or after capacitors

I do not understand all the subtleties, and I would like to ask - which option is best for connecting to ads54j40. Can i use HSDS output?