Hello,

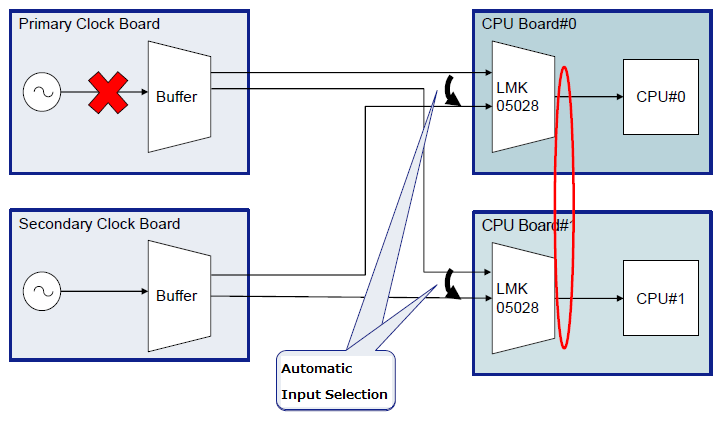

My customer is considering using the following configuration.

・ Even if one of the clock sources is lost, the LMK05028 is expected to switch to one of the clock sources by automatic input selection.

⇒ It is possible to switch.

• Expects the CPU to operate synchronously when switching occurs.

⇒ Whether or not to operate synchronously depends on the requirements of the customer's system.

[Q1]

Is the above usage assumed as a device?

I think the above usage is a special usage.

[Q2]

The customer expects the output frequency during a switch over event to be the same between devices.

Their idea is as follows.

If the input to the same PLL IC is switched to the same Reference Clock, the behavior of the PLL IC is the same.

That is, the output fluctuation is the same.

I believe that the following factors contribute to variations in PLL operation.

・ KPD

・ Z (s)

・ KVCO

・ Initial state of input

I think LMK05028 is DPLL, so there is no variation in KPD Z (s) KVCO.

In that case, I think that there is a reason for the customer.

However, the initial state variation is an external factor and needs to be evaluated by the customer.

There is no spec that characterizes the fluctuation of output at the time of switchover.

Is my understanding correct?

Please tell me if you have any questions.

Best Regards,

Kaede Kudo