hi dear supporting team,

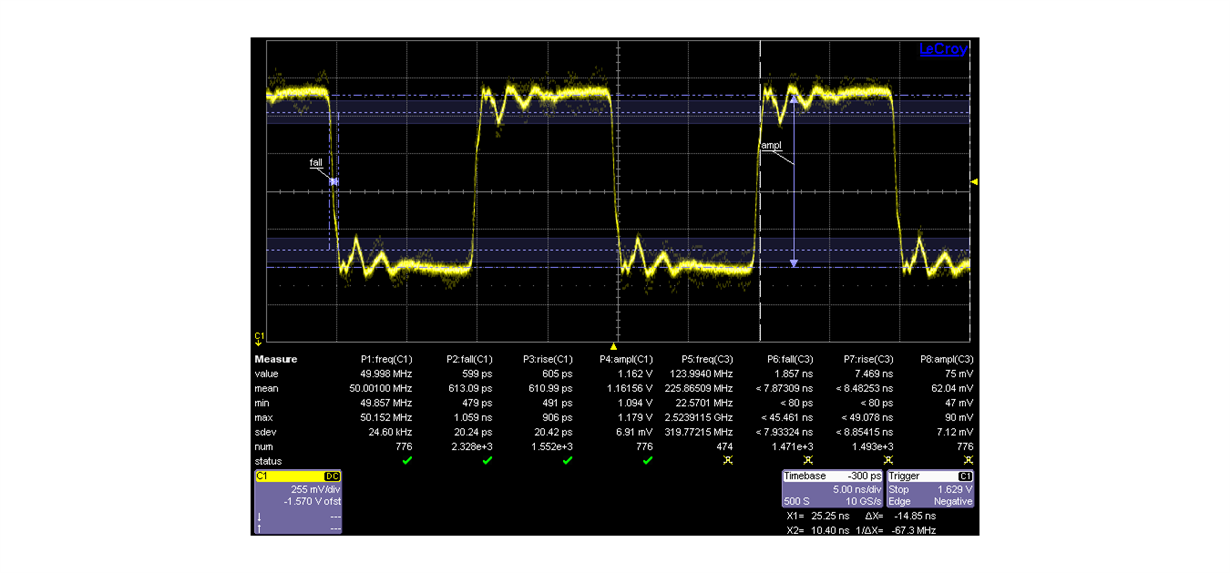

customer use SE input for LMK00304, but they found there is glitches at CMOS input of LMK00304, so could you pls help on:

1. how big glitch will affect the output performance? (jitter and etc)

2. the input threshold spec only have max and min value for Vih&Vil. what's the min value for Vih and Max value for Vil?

tks a lot!