Hi colleagues,

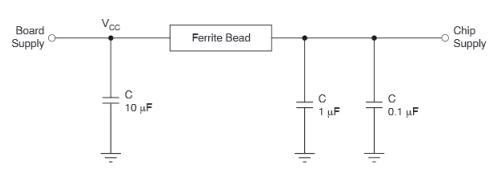

According to the datasheet, the recommended power supply decoupling method is to use a 1uF capacitor on the board supply side and 10uF + 0.1uF capacitors on the chip supply side. It is not a typo, right?

I have checked the design of the EVM of CDCLVD1204. 4.7uF is used on the board supply side and 4.7uF + 0.1uF are used on the chip supply side.

A similar strategy is deployed on the EVM of other ICs in the same family, like 10uF on the board supply side and 10uF + 0.1uF on the chip supply side.

It would be grateful that you can confirm the recommended power supply decoupling method for CDCLV1204 here. Many thanks in advance!

Best Regards,

Qipeng