Other Parts Discussed in Thread: CDCE6214-Q1

Hi,

Our products have many different configurations, we should live program CDCI6214.

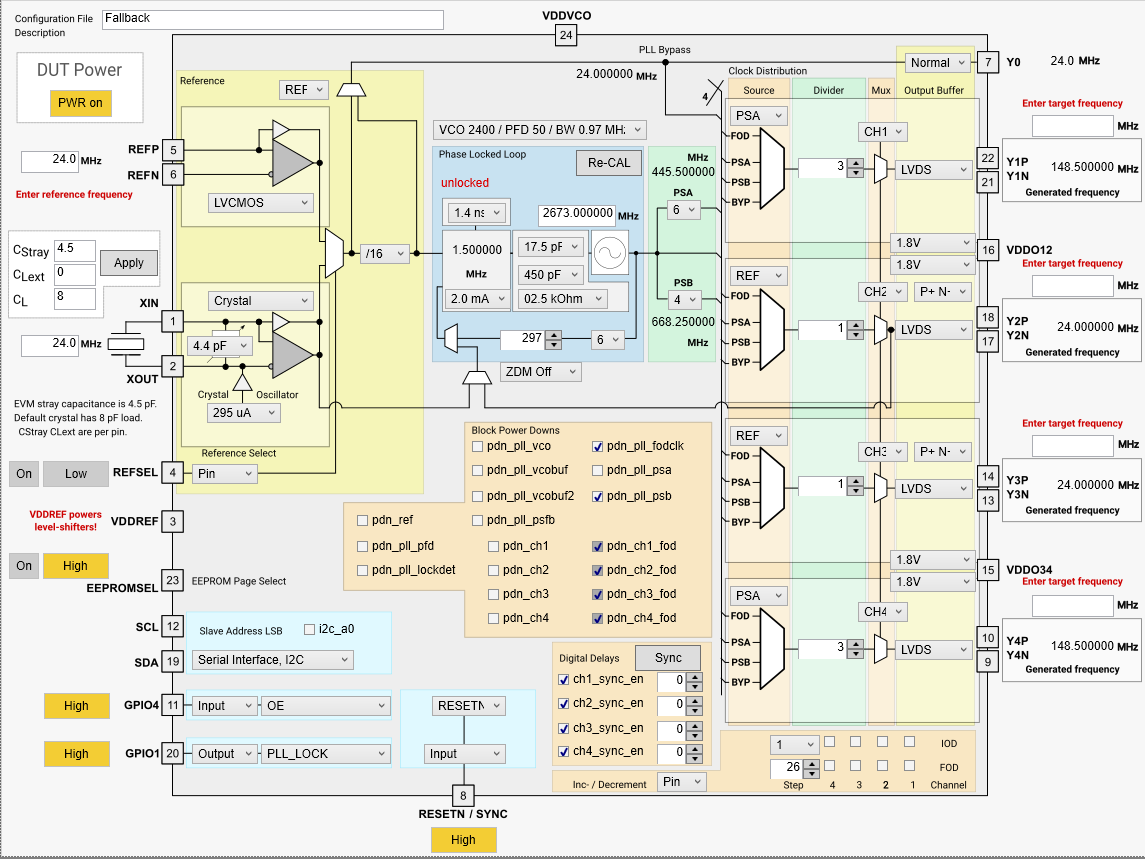

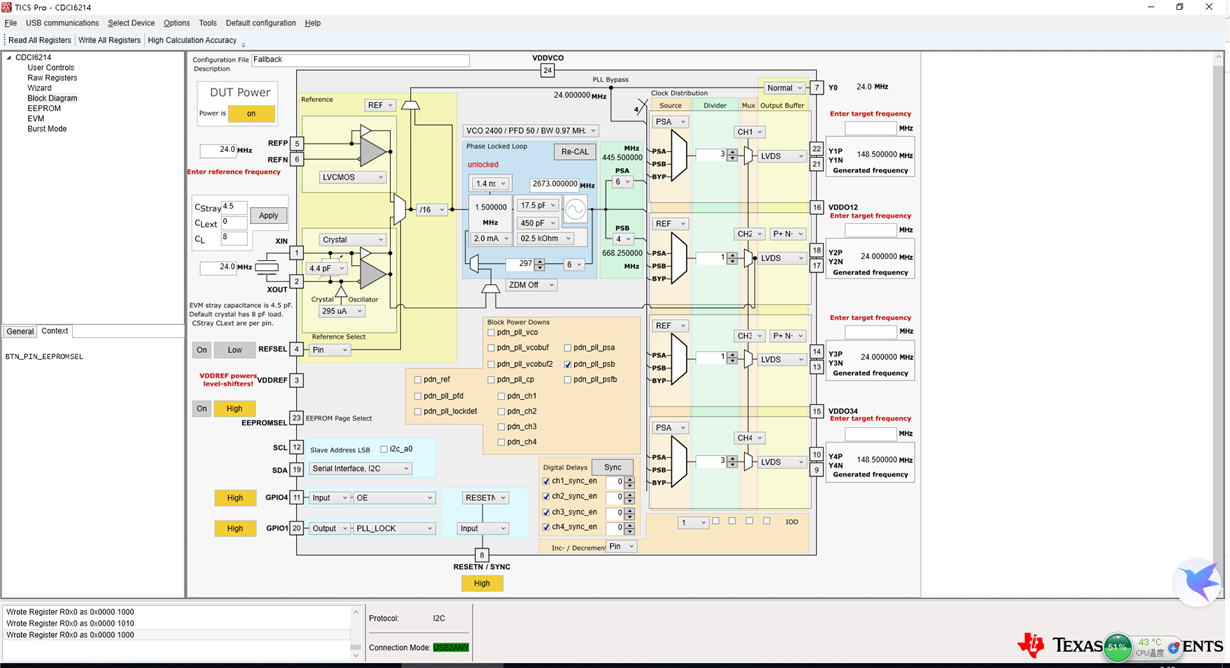

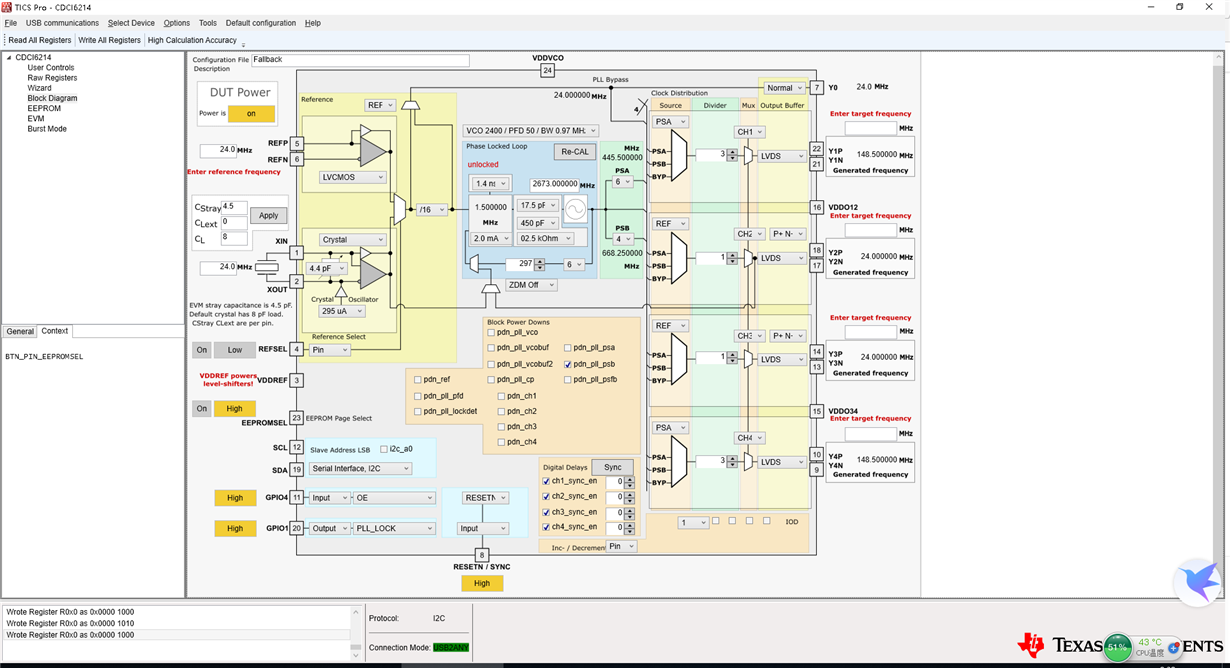

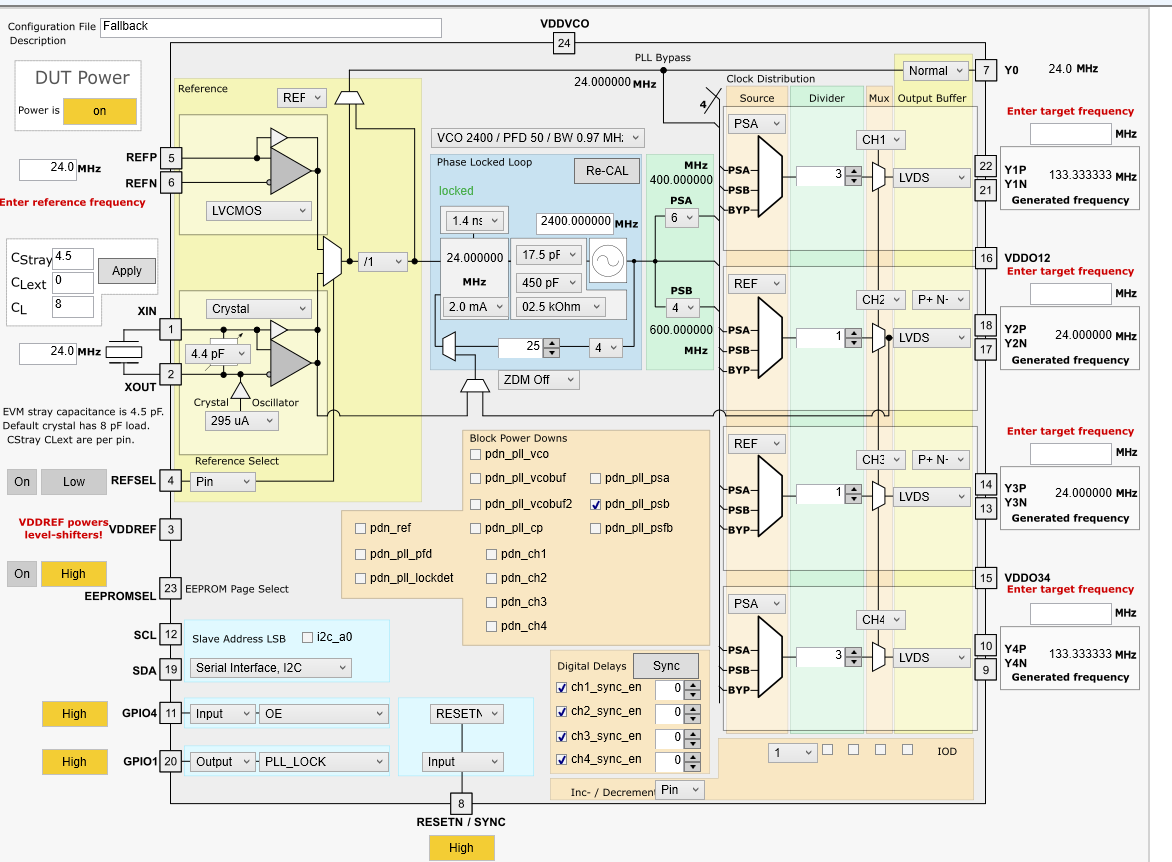

During production, we found that some devices , the PLL is unlock as shown in the figure below. but other configurations are work .

We checked that the input signal was normal. And then ,We put this chip on the EVM board, and the problem remains.

As the figure below,

step1. write all register , PLL is unlock

step2. Press "Re-Cal" , PLL is also unlock

Oscilloscope test out that all 24Mhz is out put normal, all 148.5Mhz is abnormal.

Our configuration is refer to the datasheet.

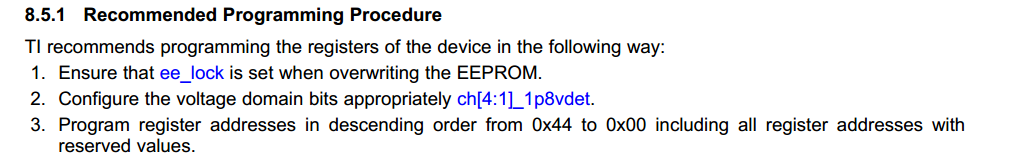

Are there any problems in the following processes??

step1. ee_lock

step2. ch[4:1]_1p8vde

step3. Program register addresses in descending order from 0x44 to 0x00

and we have step4. "RE-CAL" the PLL