Part Number: LMX2595

Other Parts Discussed in Thread: LMK04208, CDCLVP1102,

Hello,

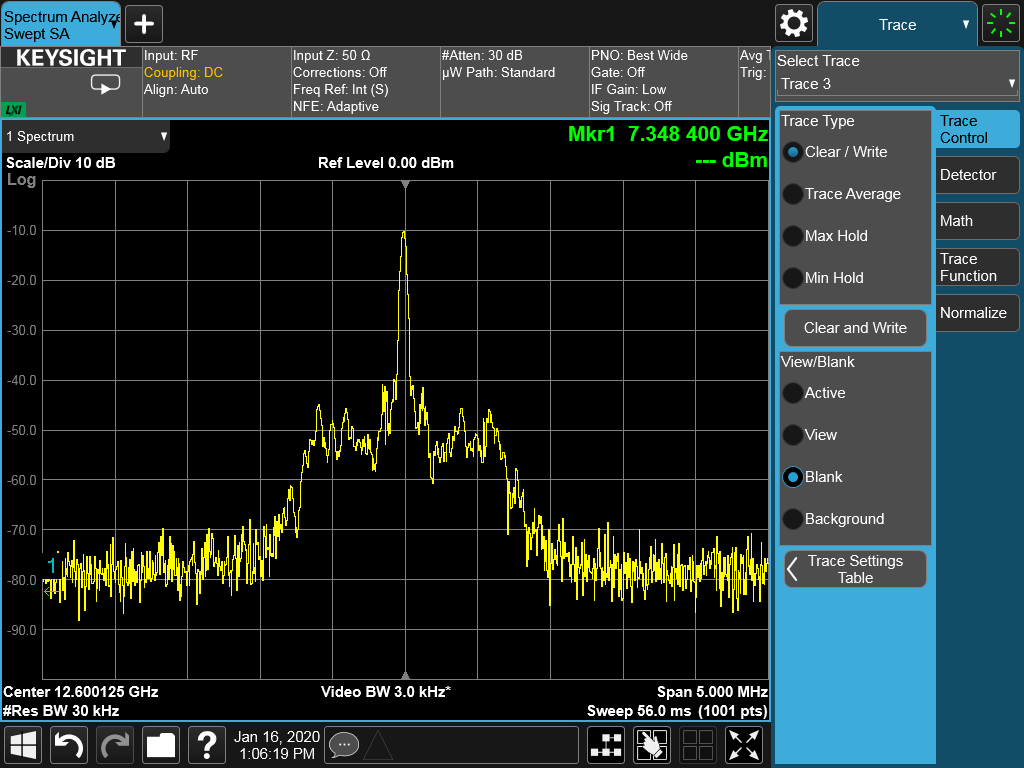

We're seeing high amplitude noise and spurs, modulated around the carrier up to around +/-600kHz. See picture attached. And also sending the TICsPro file for our configuration.

The LMK2595 is driven by a 122.88MHz clock source generated out of an LMK04208 clock distribution chip (Single ended output out of LVCMOS driver)

That reference signal then gets sent to a dual output clock buffer CDCLVP1102 via a balun. The reference signal gets sent to 2 separate LMK2595 PLL chips.Both PLLs have similar output noise issue.

Do you see an issue with the reference signal clock circuit used here or have suggestions on possible root cause?

Thanks and let me know if you need additional info.

Best,

Cecile