Hi guys,

I've put together a CDCE925-based oscillator on a Roth Elektronik TSSOP16 prototyping board. This consists of the chip, a 13.876MHz crystal, and a bunch of wires. The programmer I'm using is a homebrew version of the TI CDCE925 Performance Evaluation Board programmer (page 24). I2C pullups are 2x10k to 1.8V (though I've tried 3.3V as well).

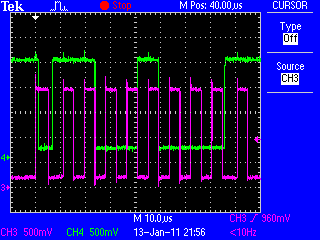

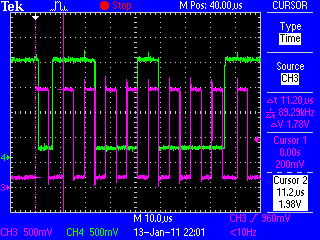

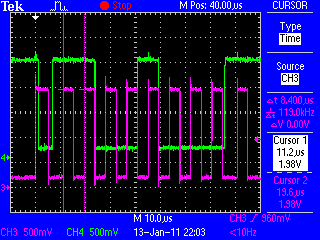

The problem I'm having is that while ClockPro can see the programmer pod -- there are start pulses and address bytes going over the I2C bus -- the chip isn't ACKing the address bytes. This means ClockPro doesn't list it as an available chip -- or rather it tells me that I should pull VDDOUT to ground. I have already done this (in fact, I've tried grounding and connecting to +3.3V) and the chip is still ignoring everything I send it.

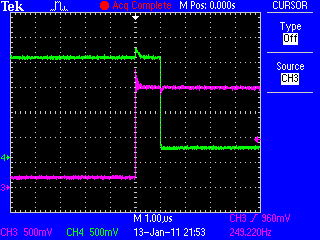

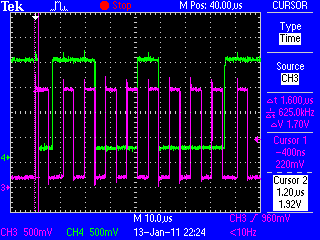

I've checked the signalling on my scope (200MHz Tek TDS2024B DSO) and it looks fine -- nice square edges, minimal ringing/overshoot/undershoot. I measured the bus clock frequency at about 120kHz.

All grounds and power lines are stable, and the power looks good (1.8V on VDD, provided by a NatSemi LP5951MF-1.8, 3.3V provided by my bench PSU).

I've even tried swapping SDA and SCL, and tried a new chip. Zilch, zip, nada.

Does anyone have any idea what might be going on here?

Thanks,

Phil.