Hello,

My customer would like to know an acceptable phase shift in their usage condition.

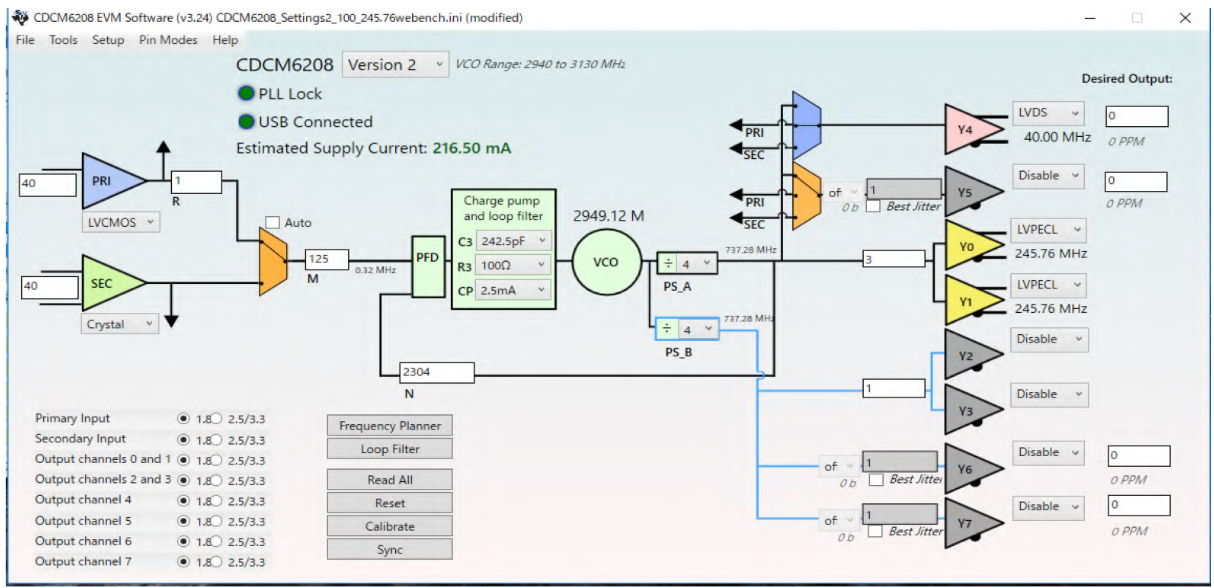

Could you tell me a limitation of phase shift for PLL lock in below configuration of PRI input(40MHz, LVCMOS)? What ppm of phase shift make PLL unlock?

Best regards,

Katsu