In order to analyze the LMK04832 overall phase noise performance for dual loop mode, I first analyze PLL1, and then export trace, and then use that trace as the source when analyzing PLL2. My question is regarding analysis of PLL1.

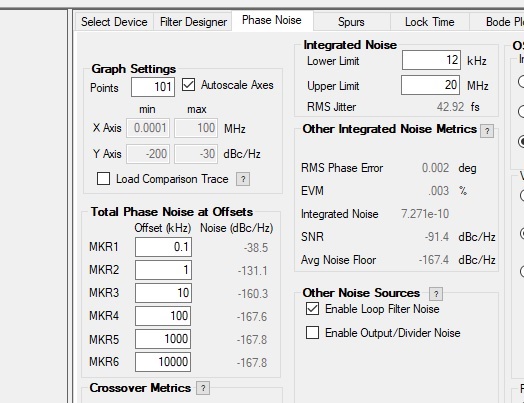

1. When analyzing PLL1 with the intent of using it as an input to PLL2, and when planning to have the VCXO frequency of PLL1 be the input frequency to PLL2, is it correct to uncheck "Enable Output/Divider Noise" under other noise sources?

Thanks