Other Parts Discussed in Thread: LMG1020, LMK04832, LMK00804B, LMK00334

Hi team,

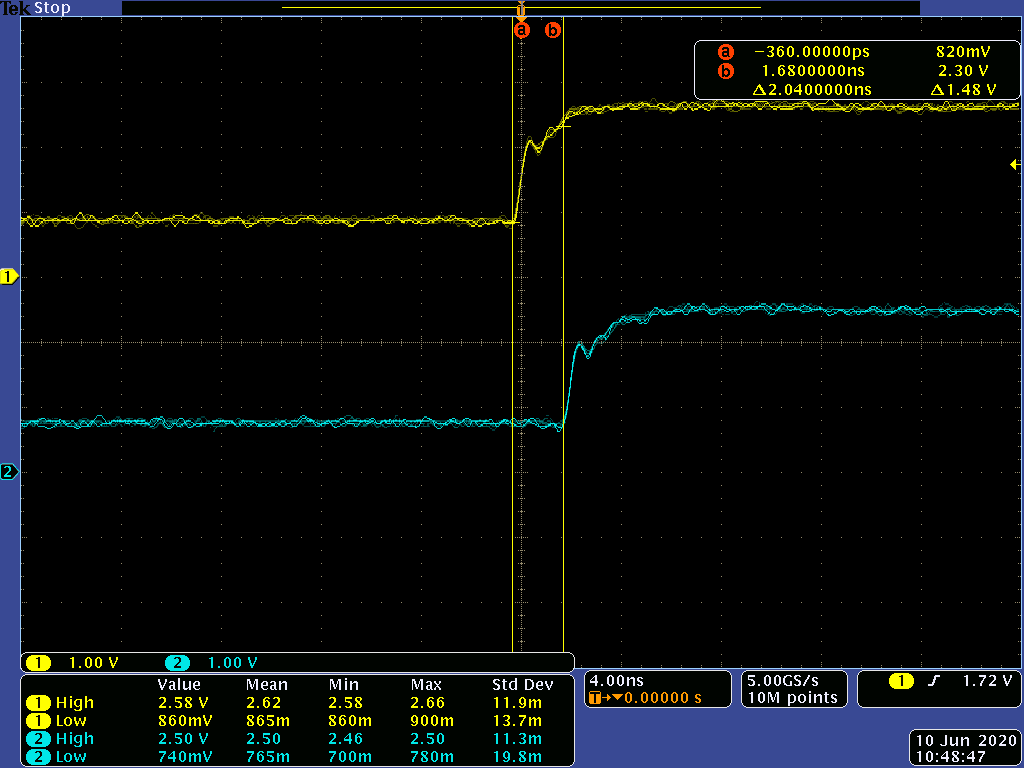

I'm trying to use LMK04821 SYSREF clock to generate a low jitter square wave to drive LMG1020. This is not a clock application, but a pattern generator. Below is output waveform of HSDS 8mA and DC coupling. The logic high/low voltage level is not sufficient to drive LMG1020, which I would like to make high voltage larger and low voltage smaller. Can I made it by resistance termination? I tried 3.5kohm termination with HSDS 8mA to get below result. Or, do we have any level shift clock buffer that can convert the output to to single-end CMOS. The delay and additional jitter is the smaller the better.

I attach the input thresholds for LMG1020 here. The accuracy of digital/analog delay of LMK04821 is much better than FPGA, so I'm trying to do this to drive LMG1020, replacing FPGA.

Thanks.