Hi Team,

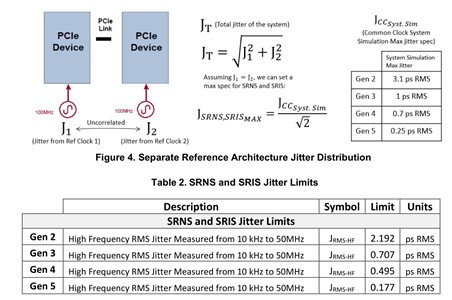

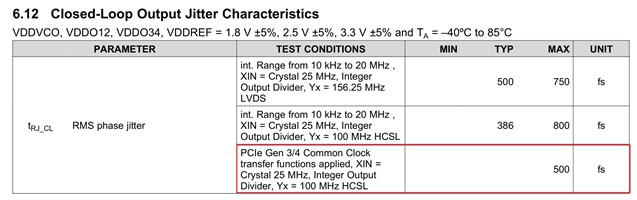

CDCI6214 100MHz HCSL output is used as Ref Cock 1 for PCIe Gen 3 separate reference architecture as shown in the picture below:

My questions are:

1. Should 500fs be used as the RMS phase jitter for Ref Clock 1? If not, what's the RMS jitter?

2. Why the maximum phase jitter for third test condition(500fs) is higher than the second one(800fs)? Because the filter for third condition is 10kHz to 50MHz while the second condition is 10kHz to 20MHz.

Thanks and Best Regards!

Hao