I've just started a few very simple simulations of LMX2594 PLL. I keep finding the quoted Loop bandwidth does not match the Bode plot and is out by over a order of magnitude.

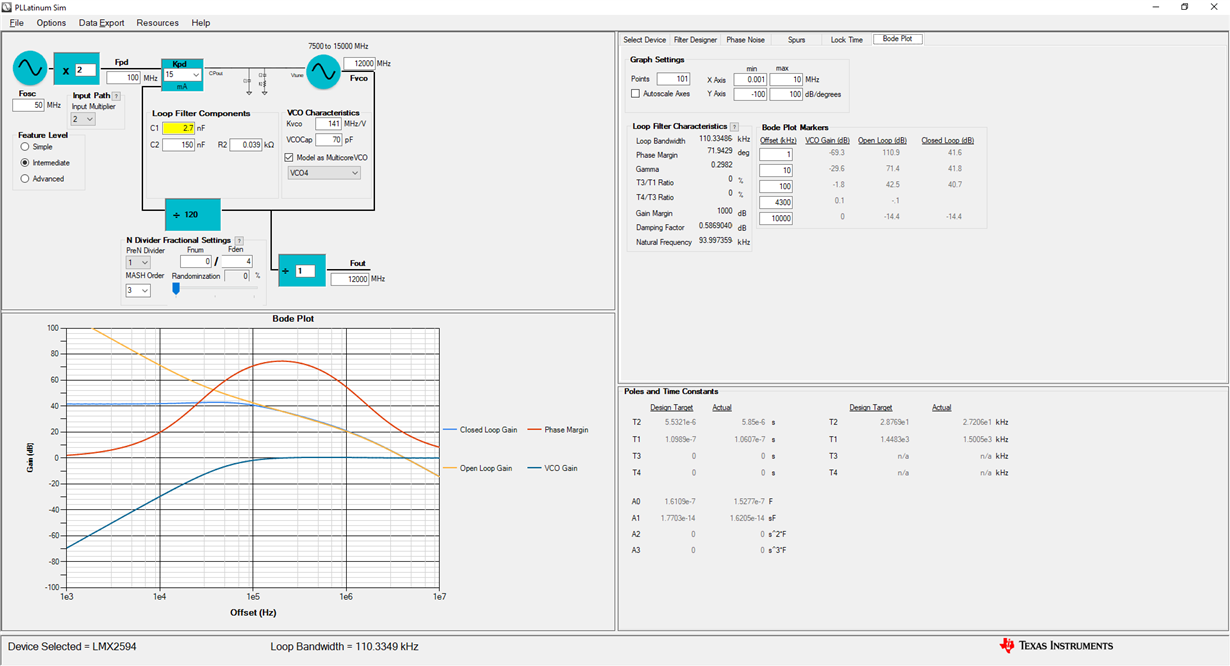

I specified a loop bandwidth of 100 kHz and phase margin of 70 Deg. Clicked Calculate Loop Filter, there were no errors like VCOCap/MinHighCap Restrict Bandwidth, new filter values appeared and phase noise changed. The summary at the bottom has a realistic loop bandwidth - 110 kHz vs 100 kHz specified, but the calculation trimmed to realistic values for R & C so this error seems reasonable.

The Bode window shows a markedly different gain in the chart and the marker data. The 0dB point is maybe 4.3MHz. The phase margin hits ~70deg at 110kHz - so that looks correct. Its like the calculated Bode gain is maybe 30dB higher than expected.

I have tried also with 3rd and 4th order scenarios and had the same issue.

Below is a screen shot of the Bode window.

Regards David