Hello,

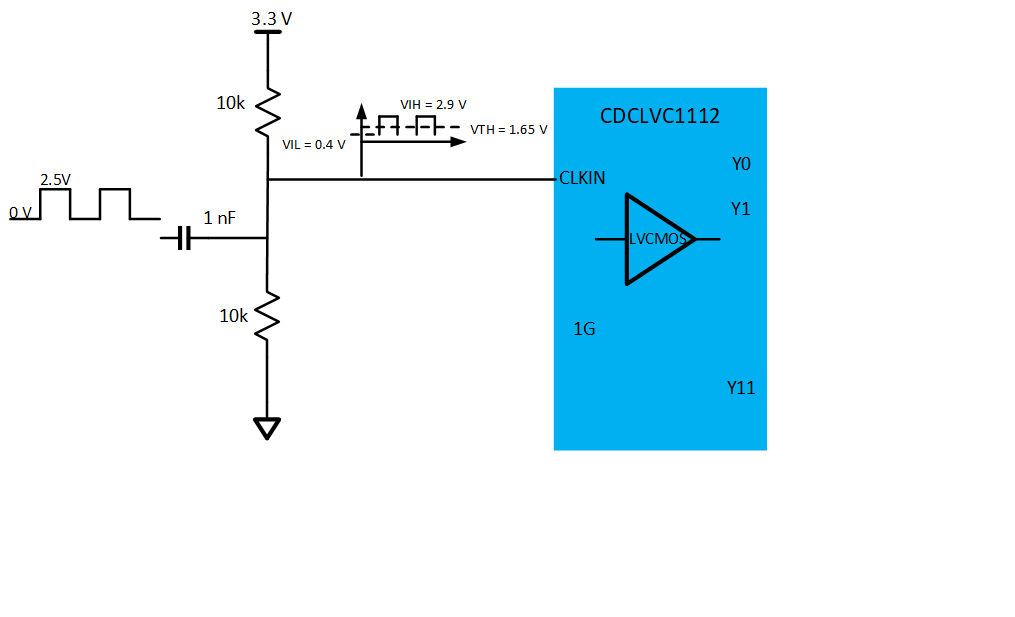

we would like to implement following circuit:

The input clock of R divider is 0v to 2.5V.

Because of start up problem mentioned in your note "How to Apply 1.8-V Signals to 3.3-V CDCLVC11xx Fanout Clock Buffer" figure 13 the resistor devider is needed (for us is not 1.8V but 2.5V). So the input specs of VDD+0.5V at input pin are met.

Question NR1: Is the thinking in picture below correct? The voltage of input clock is fix 0V to 2.5V and cant be adjusted. Output clock is referred to VDD and shall be 0V to 3.3V.

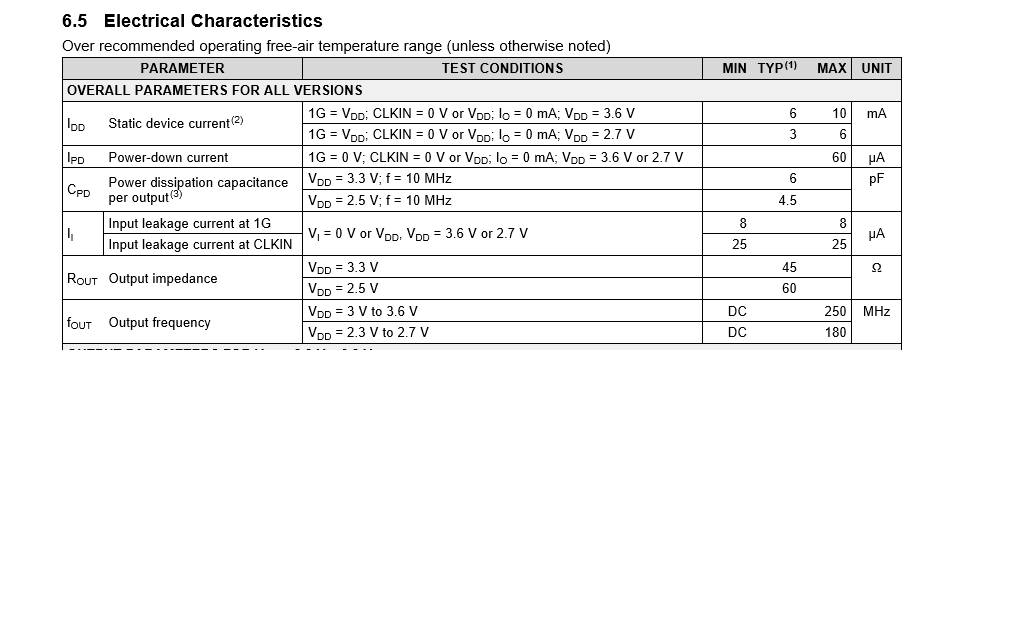

Question NR2: Datasheet cap. 6.5 -> says R_out (output impedance) is 50 to 60 Ohm for VDD=3.3V. Why is figure 5 in datasheet telling Rs=10Ohm? What should we add for 50ohms impedance controlled layout and single ended output as showed below 0V to 3.3V? In our design now is 5.11Ohm added for the output.

Many thanks in advance for your answer!

Sven