Other Parts Discussed in Thread: TIDA-01410

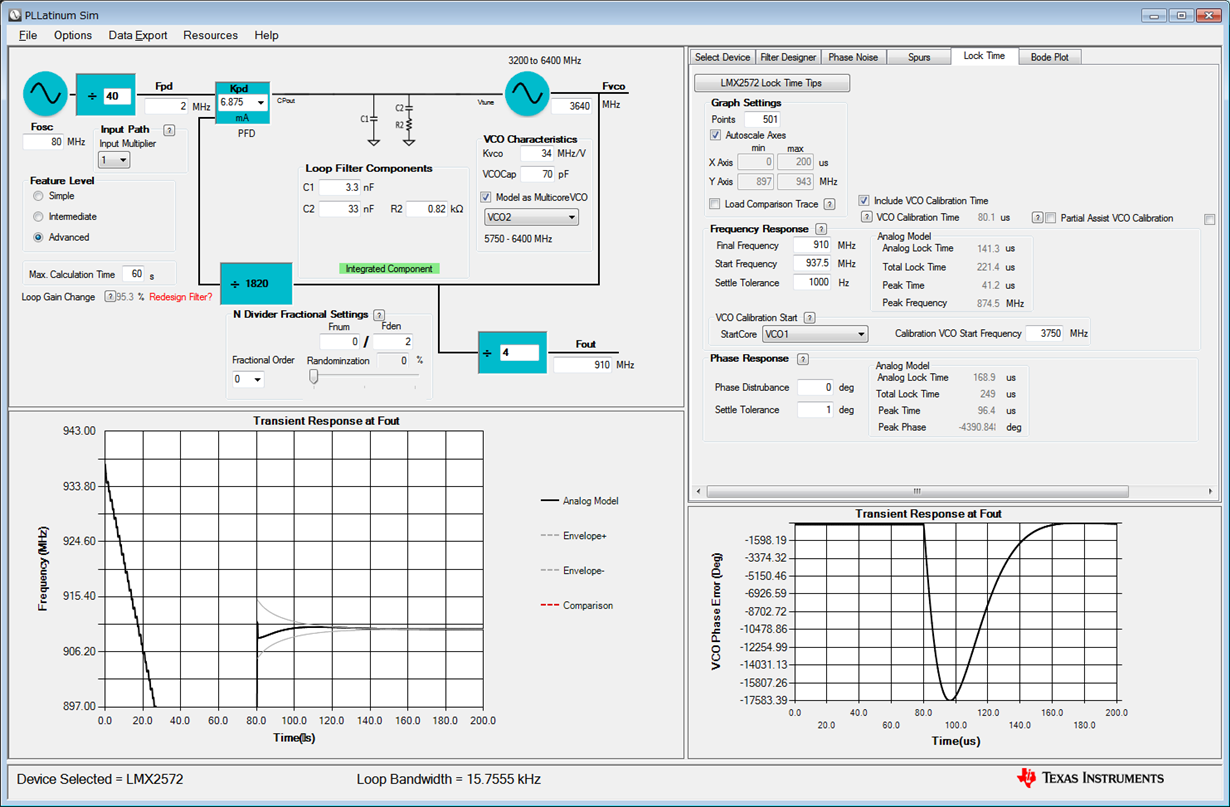

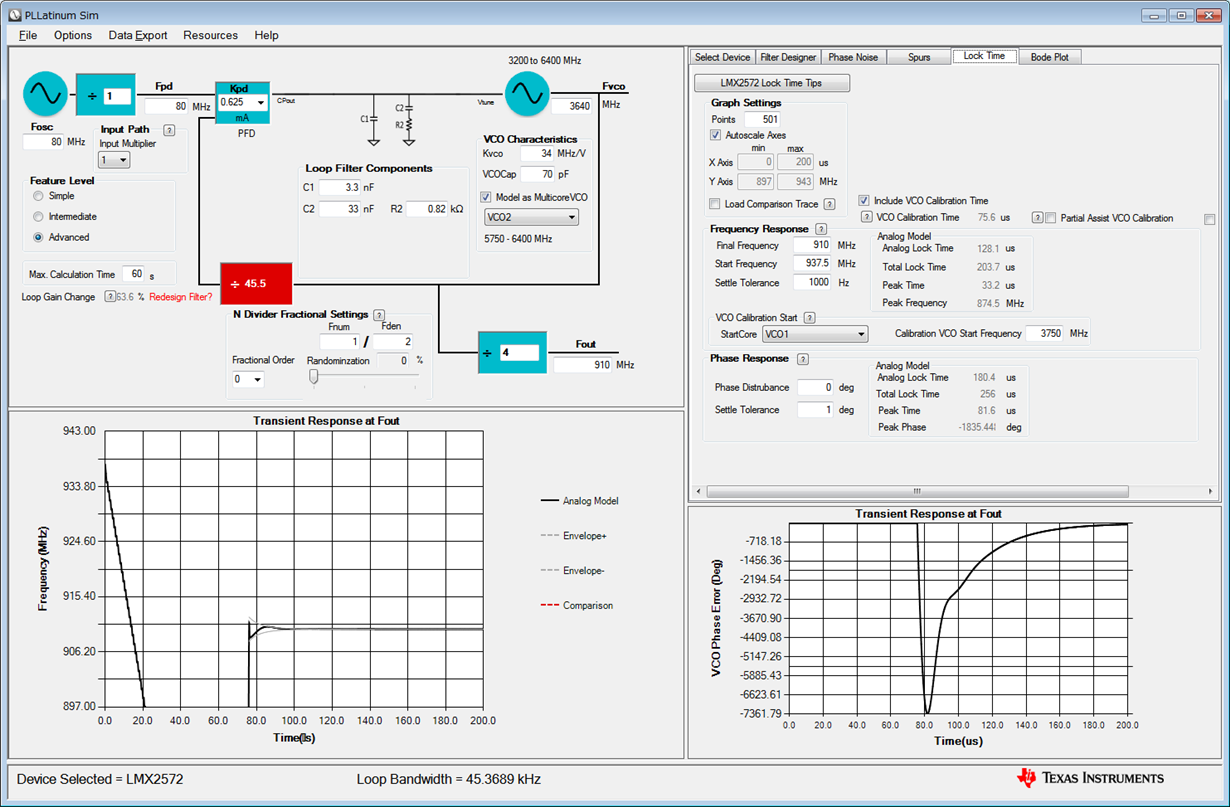

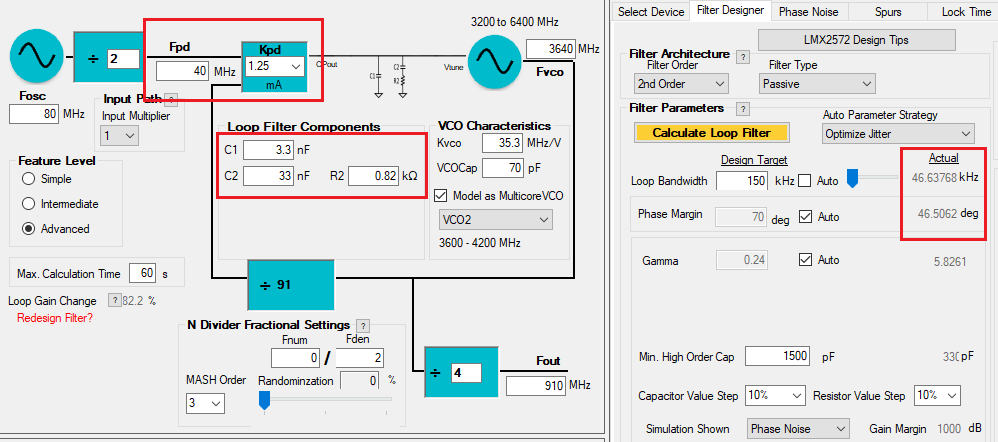

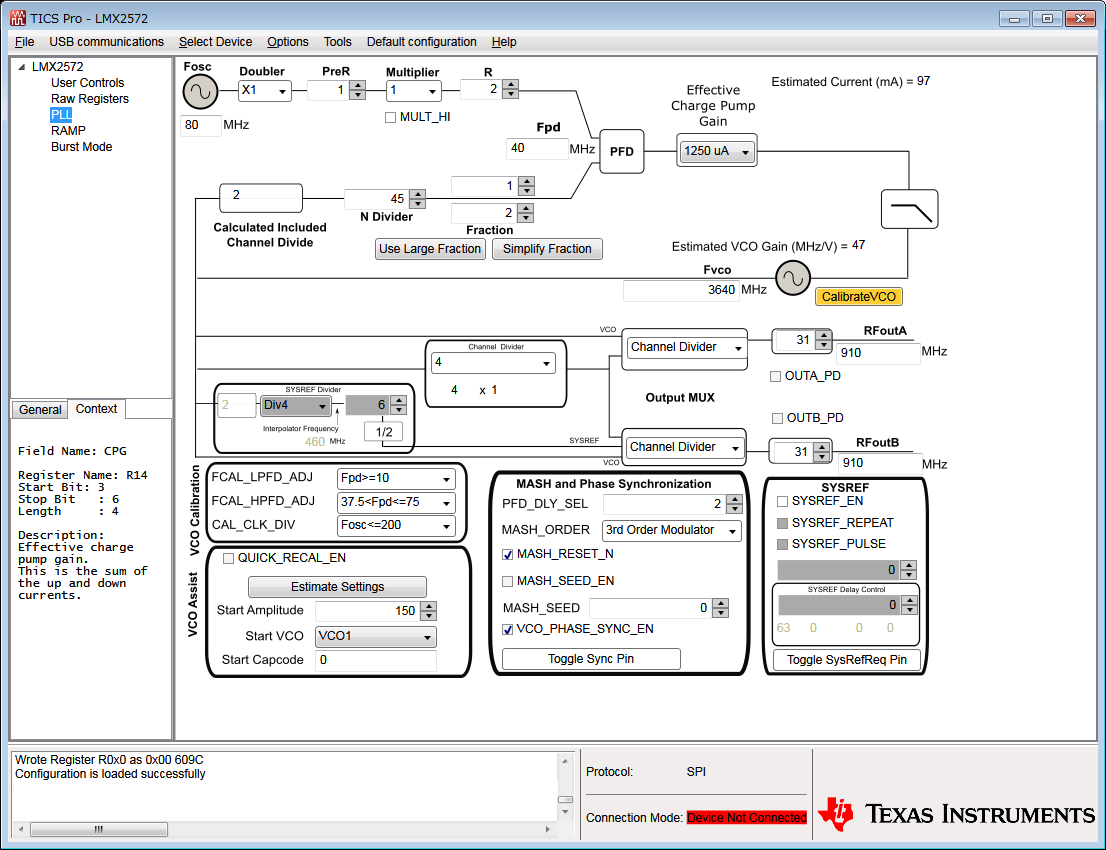

We are using two LMX2572s in integer division.

The conditions are classified as category 3 as follows.

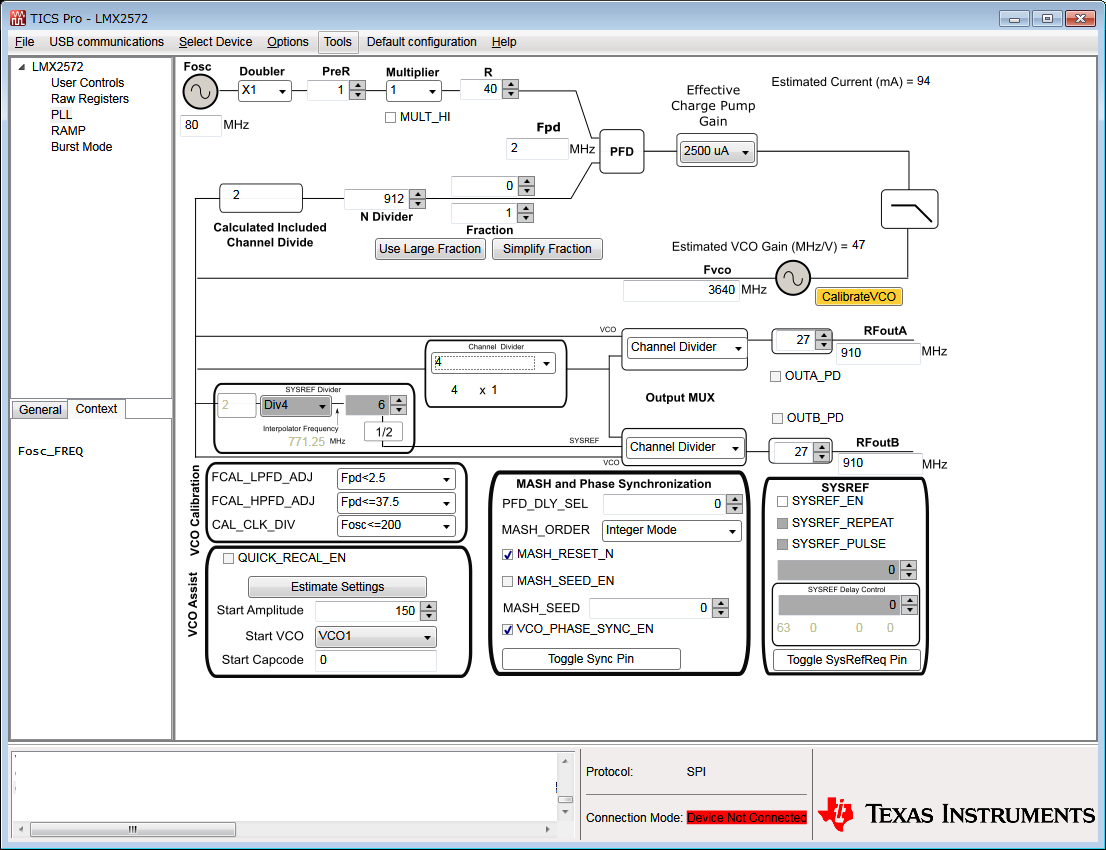

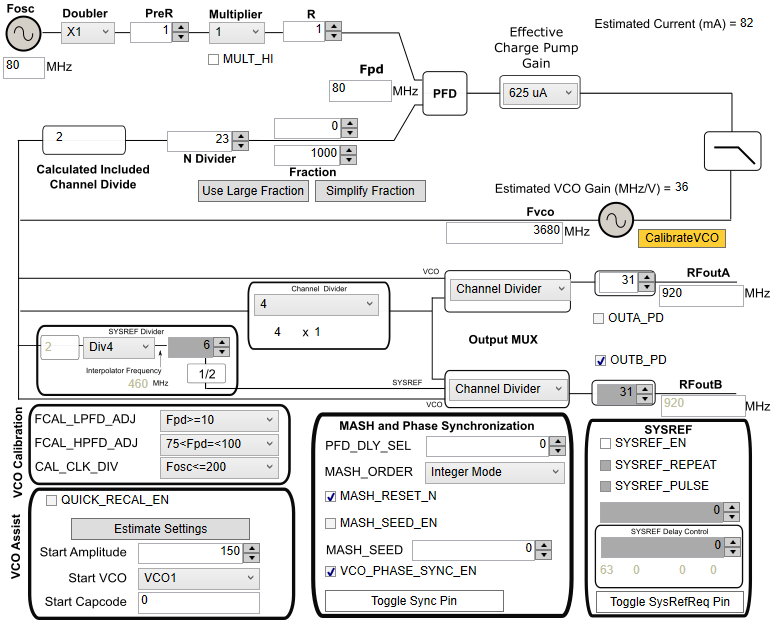

CHDIV = 4, M = 1, fout/fosc = 910M/80M = 11.375

When the phase sync function was enabled and a rising edge was input to the SYNC terminal, jitter of about 150 to 200 ps occured on one of the LMX2572 outputs. When I observed this with a spectrum analyzer, I found a spurious 6.5 kHz offset.

Would you tell me the cause and solution?

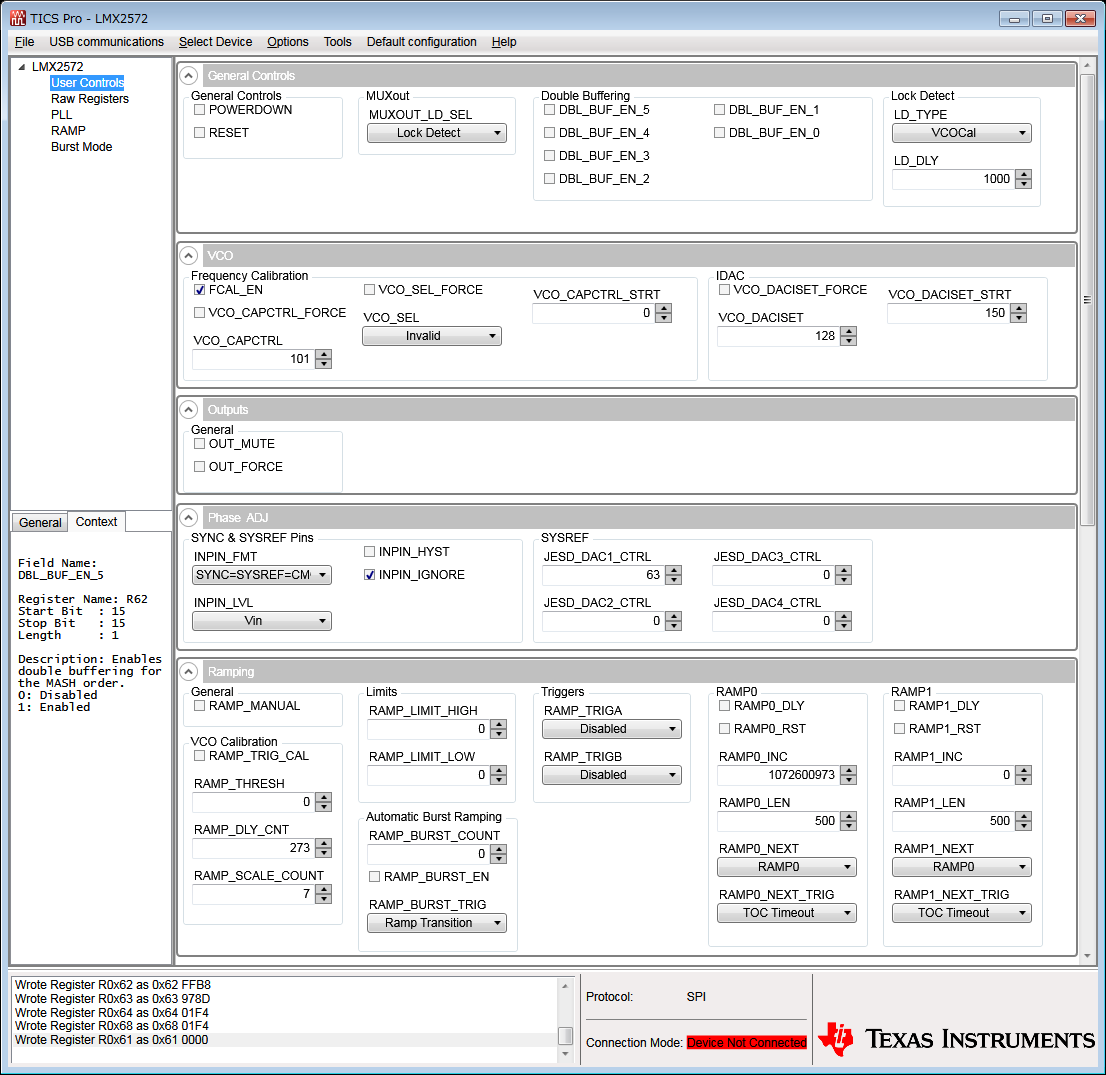

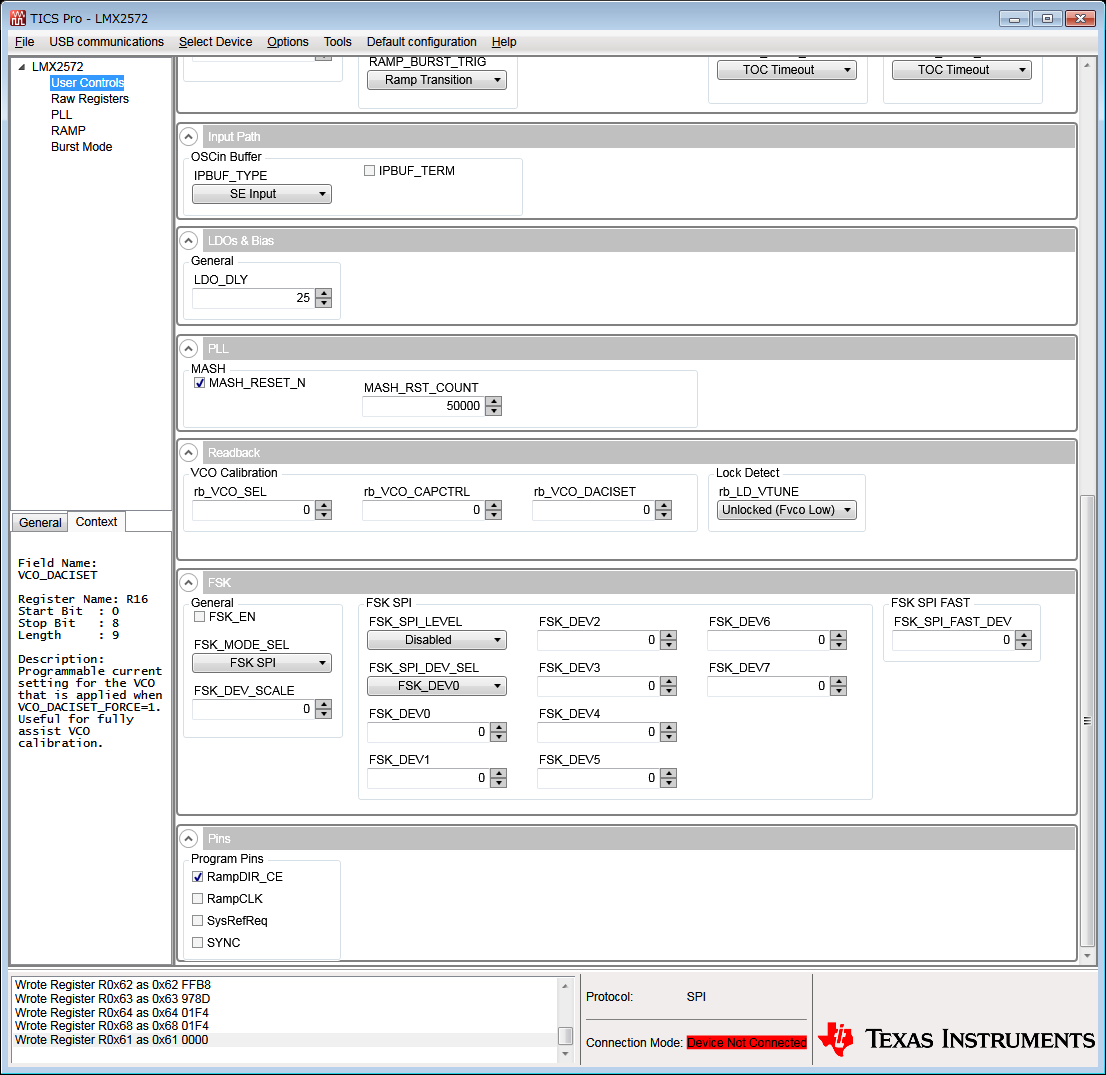

From the reference TIDA-01410 and the demo movie, the "Timing Critical SYNC Example" is set to a fractional division setting. Do I have to set MASH_SEED and PLL_DEN and select other than Integer for MASH_ORDER as described in Document 2.2.2 Theory of Phase Shift even for integer division?

Thanking you in advance.