Other Parts Discussed in Thread: CDCUN1208LP

Hi,

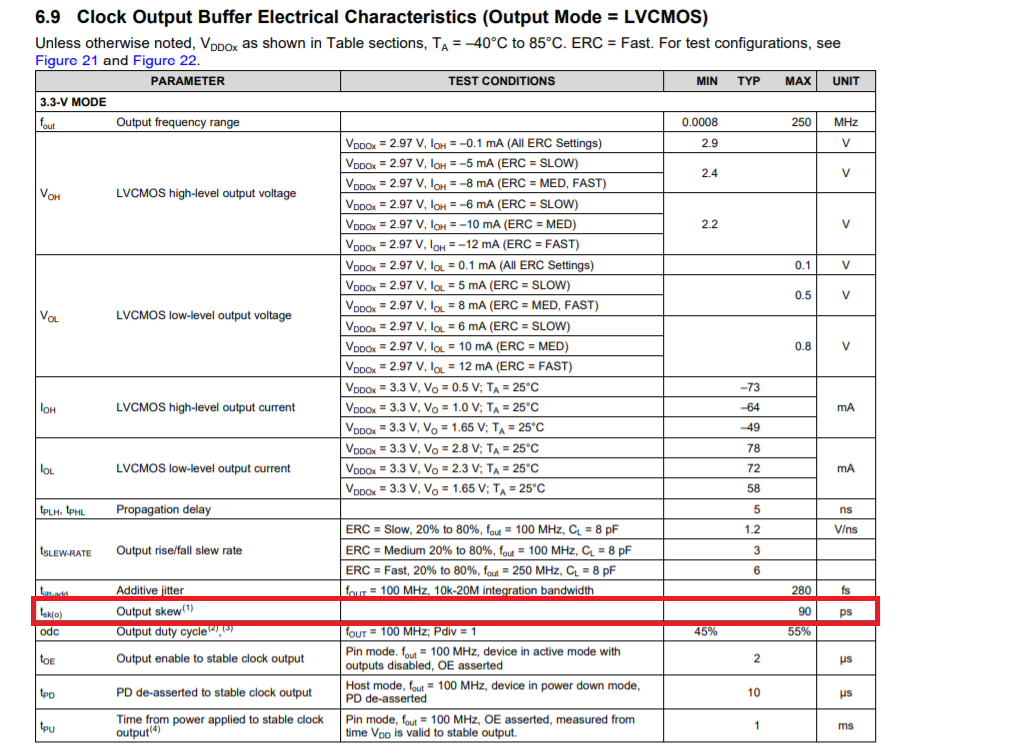

My design requires 14 outputs LVCMOS with minimal jitter.

All outputs are at 40MHz and must be synchronized. Input is also 40MHz but can be changed.

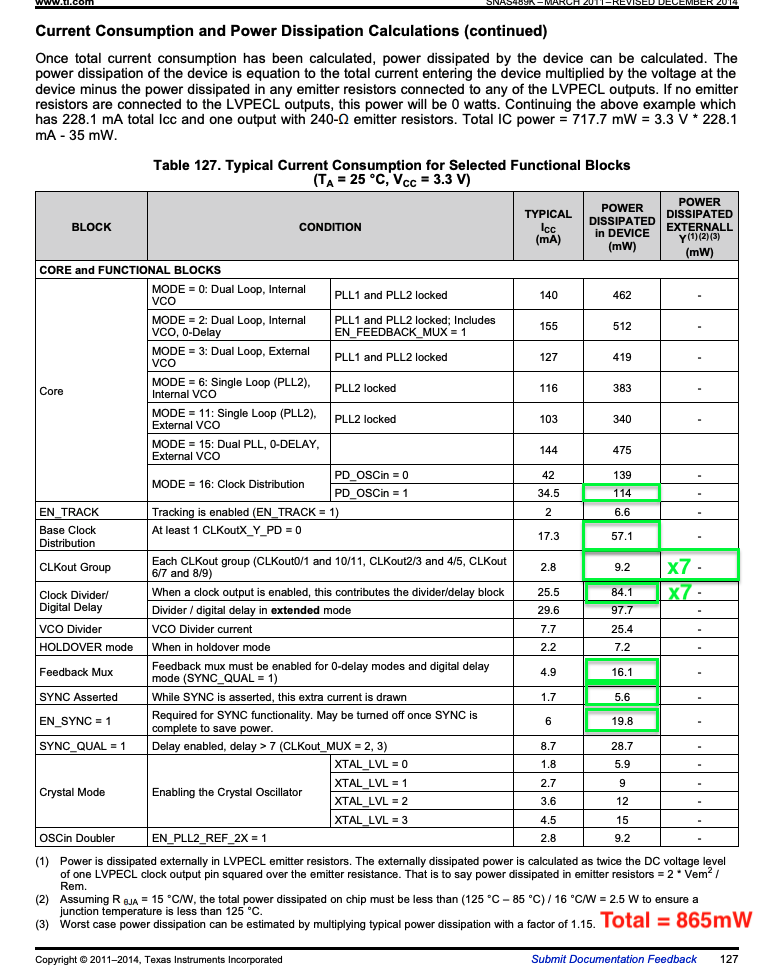

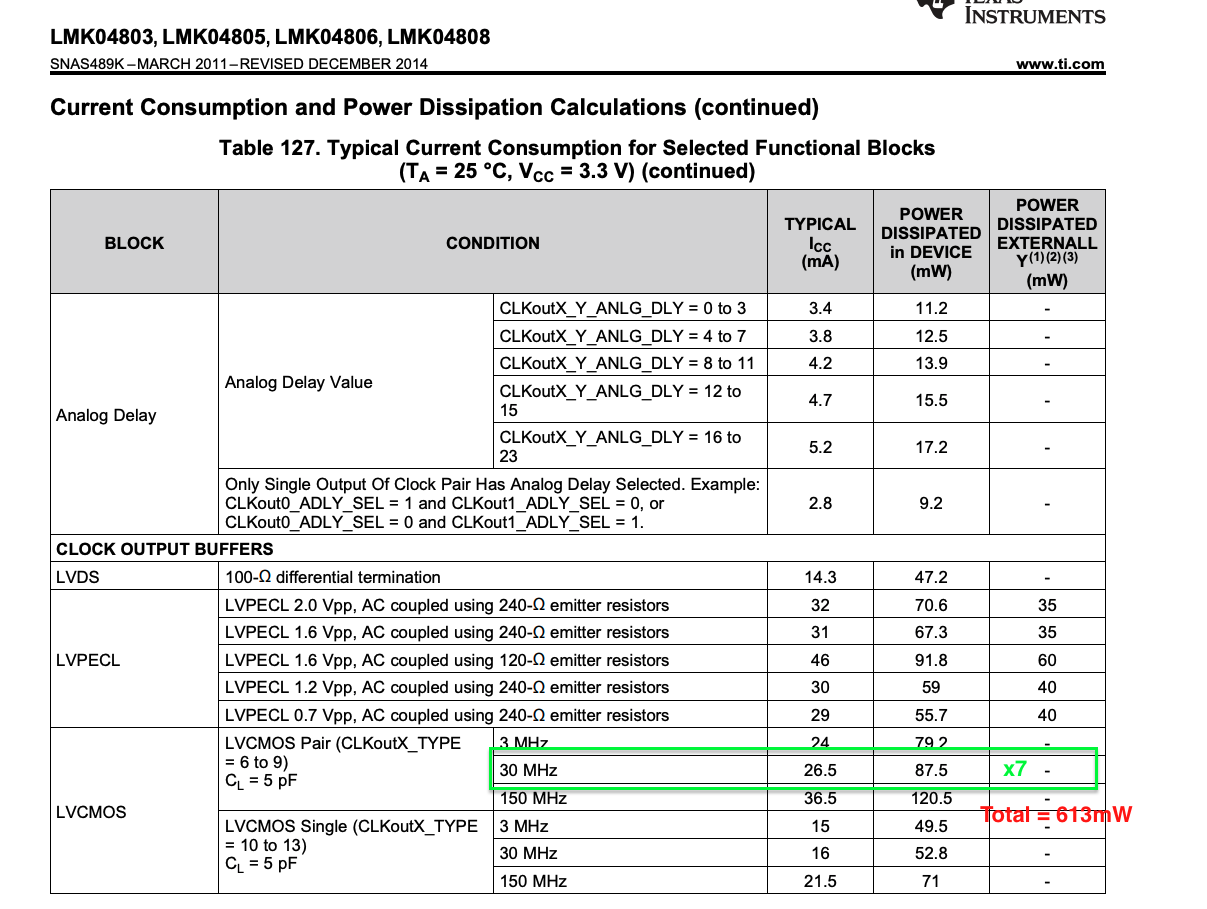

I calculated 865mW + 613mW (1478mW) of power dissipation. See pictures below.

Is there a way to reduce power consumption? Are the calculations correct?

Is there another device that could do what I need with total power around 500mW or less?

Thanks