Hello,

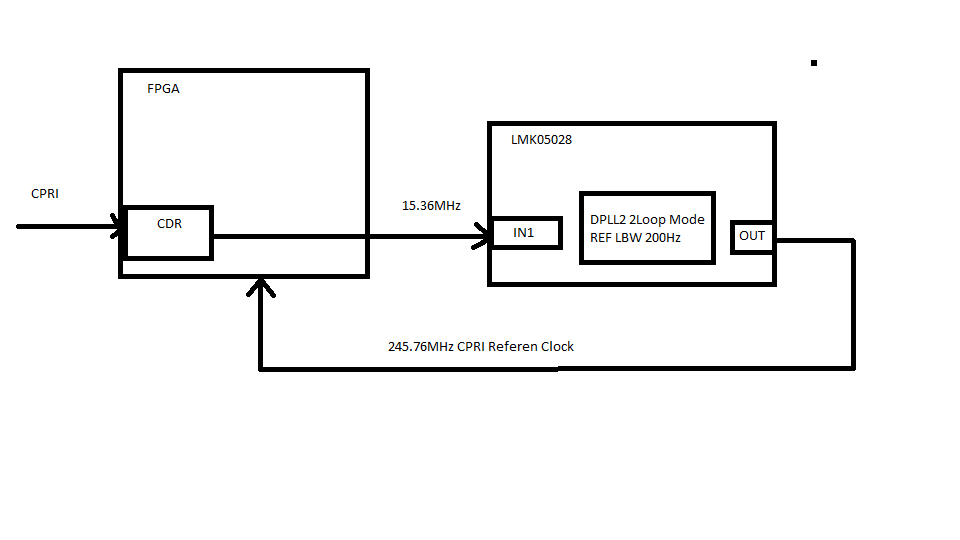

I using LMK05028 as jitter-cleaner in CPRI application as figure below and .tcs file.

Normal operation: Plug the CPRI cable at power on. CDR frequency is 15.36MHz, the DPLL2 of LMK05028 lock

Then un-plug the CPRI cable then CDR frequency drop to 15MHz (no data to recovery)

Then plug the CPRI cable the CDR frequency come back to 15.36MHz but DPLL2 freeze, not lock. I read the PLL2_status_NUM it all un-change. It seem when input reference out of pull-in range of DPLL (about 2000ppm calculate from PLL2_status_NUM read back when PLL2 freeze) the PLL freeze and can't recover.

What would you suggest to solve the problem? so PLL can auto recover.