Hi,

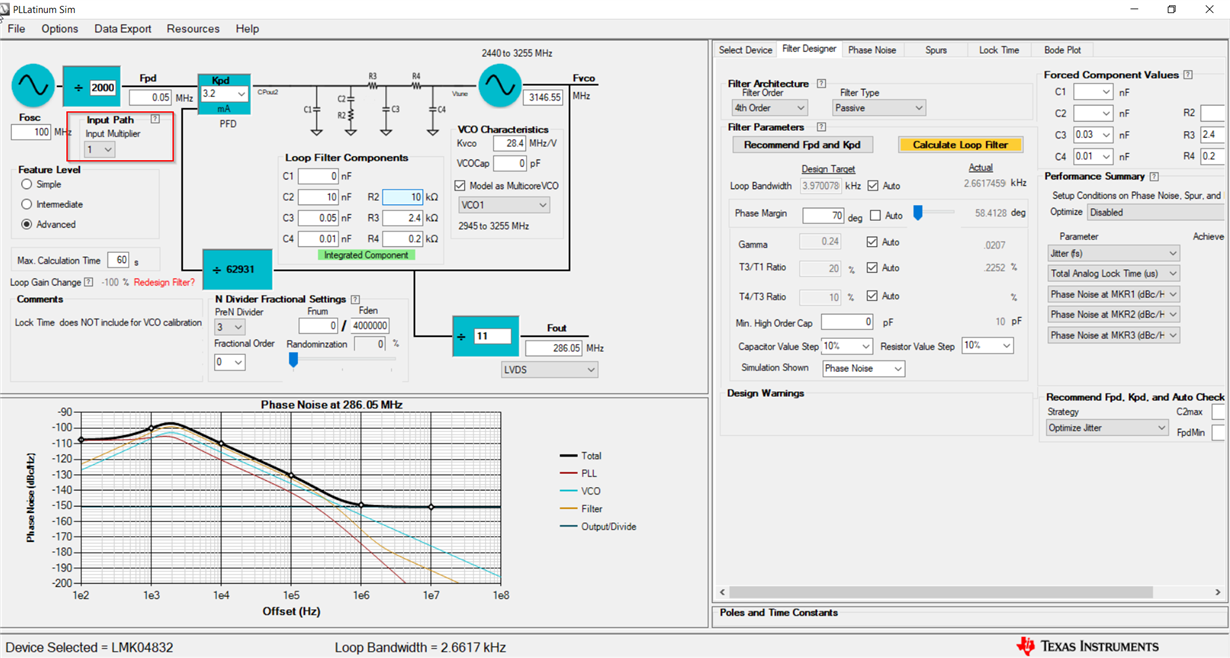

I faced a problem in locking PLL2 when I enabled the doubler. The configuration is shown as below:

From the datasheet, I saw that enable double can get better phase noise result and in some of the previous design that use LMK04832 had also enable the doubler but didnt not face any issue. But for my case, when i enabled the doubler, the PLL2 unable to lock. If i disable the doubler and change the R2 divider into 2000, the system able to lock. This sounds weird to me as i thought enable double can reduce the phase detector frequency and hence should able to lock easily than that without doubler.

I also attached the image for PLL2 loop filter parameters, from PLL Platinum the phase margin looks good and jitter also very small. I doenst sure what cause the PLL2 unable to lock in this case. Besides that, I wondering how to use the input mutiplier in PLL Platinum Sim, I initially thought it is refer to the doubler, but it seems it is not. Can explain more to me how to use this input multiplier as well? Thanks.