Other Parts Discussed in Thread: LMX2594

Hi Team,

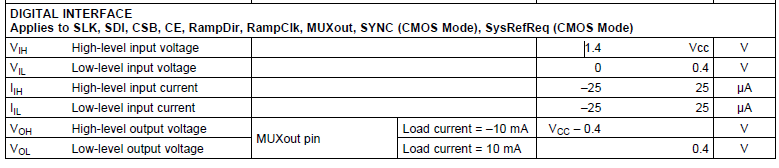

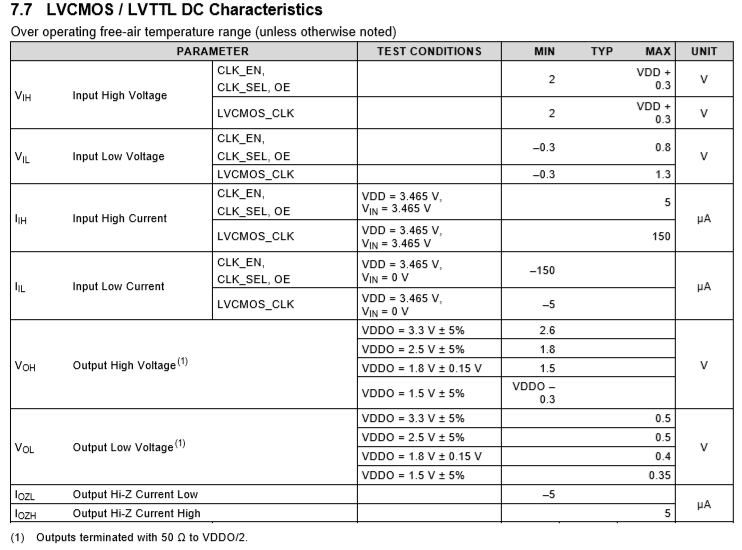

We are using LMK00804BPW as synchronizer for 3 other LMX2594RHAR. The Q outputs of LMK are directly connected to the SYNC inputs of LMX without any series resistor or pull-up on the lines. A note in datasheet of LMK states: "Outputs terminated with 50 Ω to VDDO/2." does this mean a 50ohm pull-up to be connected externally? Could you please elaborate on this note?

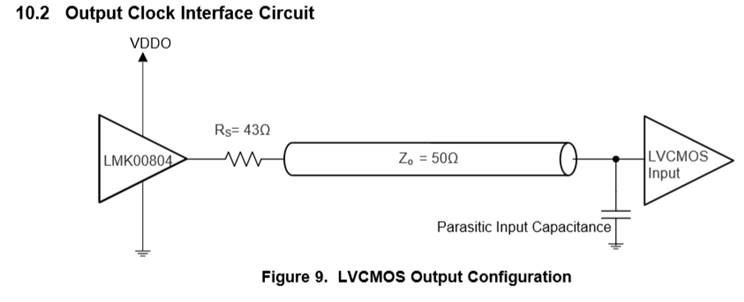

Also, In EVM of LMK, a 43ohm is used in series with the output. Should it be included in the design and how does it correlate with the 50ohm pull-up mentioned in the note above.

Thanks,

Sultan.