Other Parts Discussed in Thread: LMK05318

Hi team,

Would you kindly help me to understand the concept of DPLL compared to LMK04828?

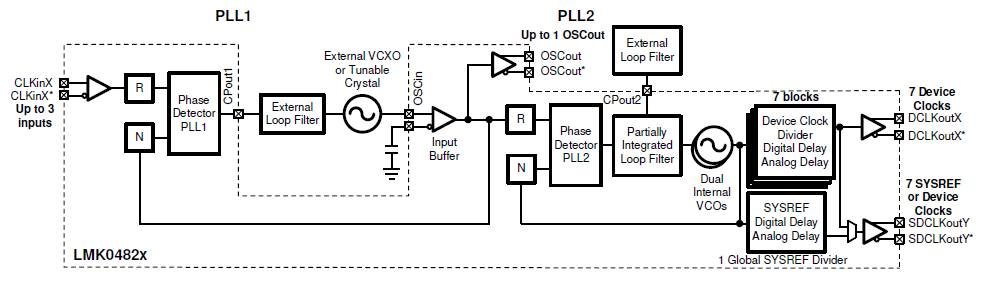

This is a simplified block diagram of LMK04828 dual-loop. PLL1 is used for jitter cleaning and PLL2 for frequency synchronizing.

This is what is mentioned about DPLL in the Precision lab, and I wonder why we need this DPLL structure other than dual APLL LMK04828's structure as I attached above.

I refered to LMK05318 datasheet to understand about DPLL. And it sounds for me like DPLL is nothing more than an alternative of PLL1 in LMK04828 structure, but controlling the N divider of the cascaded APLL in more sophisticated way than they were designed in analog, thereby making more accurate(w/o phase error) and clean(w/ low in-band phase noise) reference clock to next cascaded APLL.Is this correct and Is this the point of the reason why we use DPLL?

Your kind explanation would be so helpful for me to understand the overall clock device structure for better design.