Other Parts Discussed in Thread: LMX2820, PLLATINUMSIM-SW

Hi ti experts,

I have 3 problems of integer boundary spur(IBS) about lmx2594,

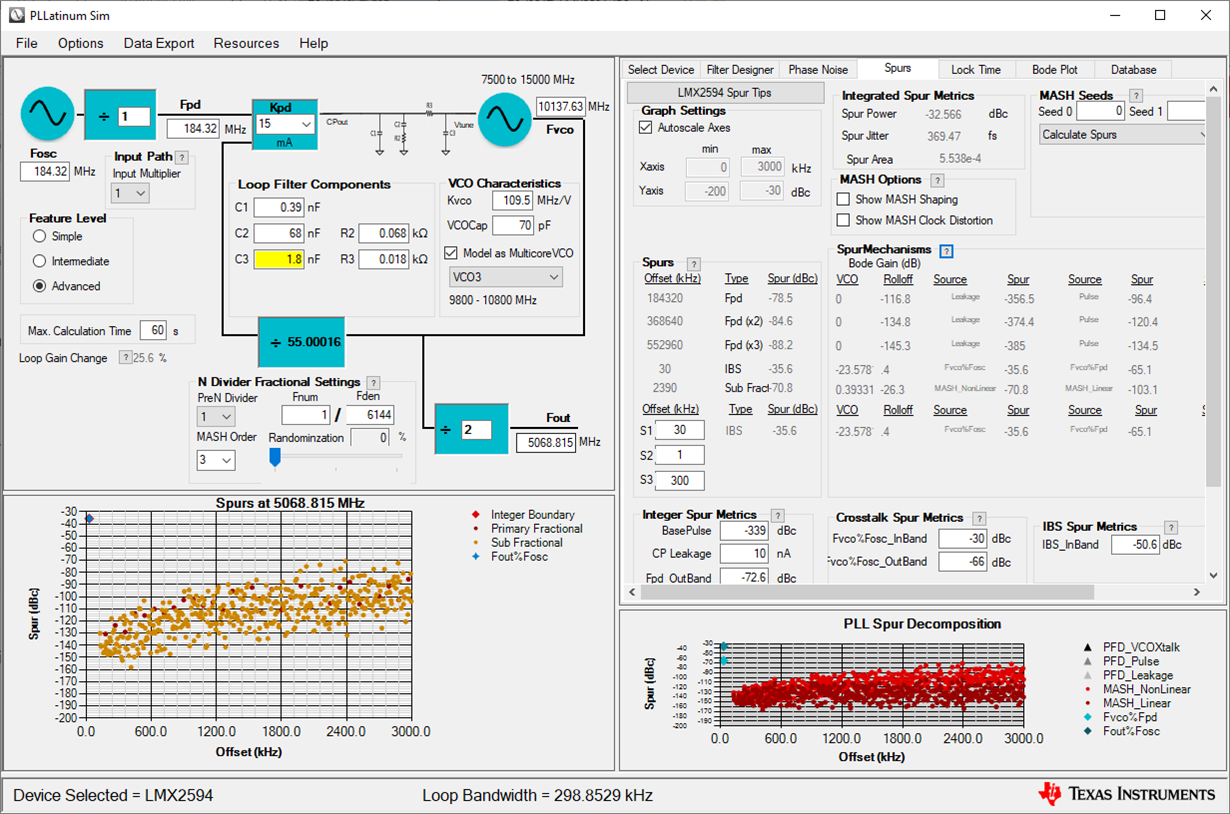

1.When i set Fpd=184.32M and Fden=184320,there is a large IBS at 30khz offset with the pll output at 10137.63M. I can understand 30K IBS here.

To avoid this IBS at 10137.63M, i changed Fpd to 221.184M,but there is still a 30khz spur at 10137.63M. I don't know why the spur still exists.

From my understanding,Fvco/Fdp=10137.63/221.84=45.833469 which is not close to an integer channel,so there should be no integer boundary spurious.

2.Is there any other methods to avoid IBS?

3.How to distinguish IBS of pll dominated or VCO dominated?

Thanks.