We have designed a custom PCB that uses an LMX2594 to generate some higher speed clocks from a 10 MHz reference and are having problems. We built two of the PCB's, on one of the PCB's the LMX behaves as expected. Powers on correctly, can be configured as expected, locks and generates the clocks we expect.

The other PCB we are having nothing but issues. When we first received it, the LMX seemed to function correctly, it would configure and lock from a first power on, however if you powered it off, then powered it back on, it would immediately attempt to draw in excess of 2 Amps (hard to tell exactly but it was multiple Amps) and get red hot, the only way to mitigate this seemed to be to leave it off for a significant amount of time before trying to power it on, although we didn't try enough times to confirm this was consistently right. We did try discharging all of the capacitors around it (including its internal LDO ones) before attempting the power on, that made no difference.

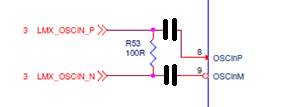

The only difference we noted was when it worked, the OSCin inputs DC level was approximately 1.5 V, when it was in its super heated state this was ~ 3.3 V (pretty much oscillating at the supply rail).

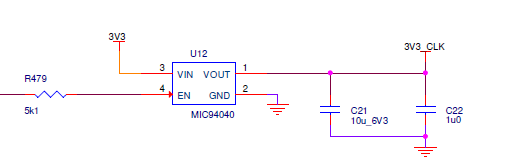

Assuming the chip was faulty we had it replaced. The second chip was worse, we couldn't get it to power on without immediately going into pulling huge current, super heating mode. We finally managed to achieve a workaround to get a consistent start, whereby instead of switching the power to this device off and on using a FET switch (which is a relatively fast turn on), we just hooked it straight to the 3.3V regulator, which has an incredibly slow start up, this then seemed to let us get the chip powered without cooking itself, however we couldn't get the chip to respond to anything on the SPI bus, so assuming we'd cooked it we replaced it yet again.

The third chip is somewhere between the two, using the same workaround (powering directly from the 3.3V regulator) we can get it powered and on consistently not melting. However when we attempt to configure it using the SPI commands we get very mixed behaviour:

- 1 time in about 20 it powers up correctly and locks.

- Normally it does nothing, the current draw doesn't really change, the OscIn DC jumps up to ~3V and when I probe the caps on the internal LDO's they are all at 0V as if its shutdown. No matter what we then set we can't get it back to life.

- Every few times, at some point during the command set the device goes into meltdown mode, pulls vast amounts of current and cooks.

From power on we can't get anything back from the SPI registers, we either get all 1's or all 0's depending on the state of the Muxout pin, if we then configure it to make that serial data out we get the behaviour as above, occasionally it works and we can read from it, mostly nothing, close second, error condition.

So my list of questions:

- Is there some power on criteria that is needed to ensure the device powers up successfully without attempting to self destruct, if so what is this.

- Is there a min / max ramp criteria for the bring up of the main 3.3V rail to avoid the above.

- Why would the OSC in DC bias jump from normal ~1.5V to ~3.3V?

- Why does there appear to be an SPI command that can cause it to self destruct.

- What could be causing the huge current draw and temperature rise, is there a clamp diode somewhere activated and locked on, and how / why is it doing this?

Thanks for any help you can offer,

Bryn