Hello,

We observe that a reset of the LMX2492 PLL through register write fails with a failure rate in the order of 1%.

We reset the device by the following writes to register 2:

PLL_write(0x02, 0x04); // Register reset (same issue with value 5, i.e. w/o powerdown)

delay_ms(1); // Delay

PLL_write(0x02, 0x01); // Set PowerDown to '01' (steady on)

_delay_ms(1); // Delay

{...} // Load MUC, FRAC, CPM, COUNT registers etc...

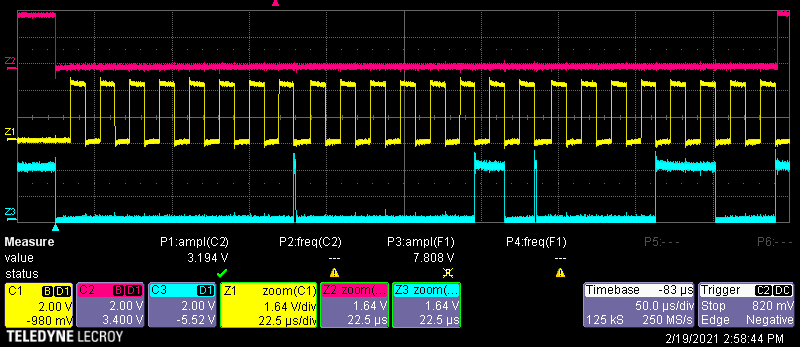

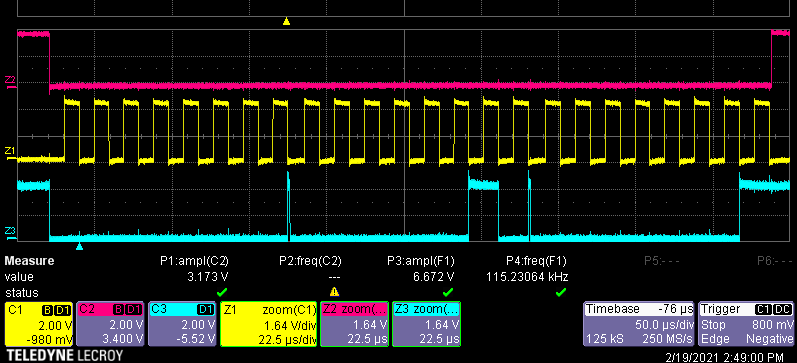

We define failure to reset by not receiving a frequency signal out of MUXout, which is set to "Output N Divide/4" (MUXout_MUX=19, MUXout_PIN=2, set by PLL_write(0x27, 0x9A)). Instead, MUXout is constant high.

We also observe that in the failed state reserved registers 46..55 (0x2e..0x37) read 0x00, while those registers read non zero values after successful reset and initialization. Documented registers read reasonable values in any state.

We have increased delay in above code without reduction of failures.

We have increased Vcc to the datasheet maximum 3.45V without reduction of failures. Each of the four 3.3V supply pins are supplied through a LC network with a 330 Ohm (at 100MHz) ferrite bead in series with one 1nF and one 100nF capacitor close to the device , all four of those stubs powered by a single 3.3V LDO with additional capacitors.

Failure to reset can be usually resolved by repeating above reset procedure.

What can cause this behavior?

Thank you!