Part Number: LMK04828

Other Parts Discussed in Thread: LMK04832

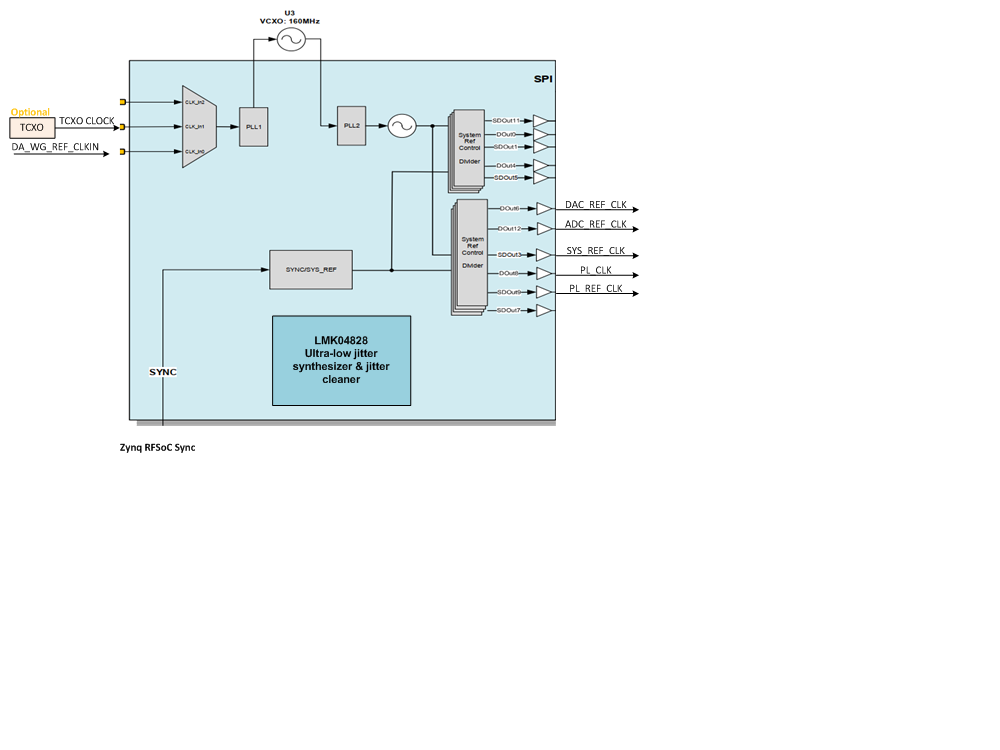

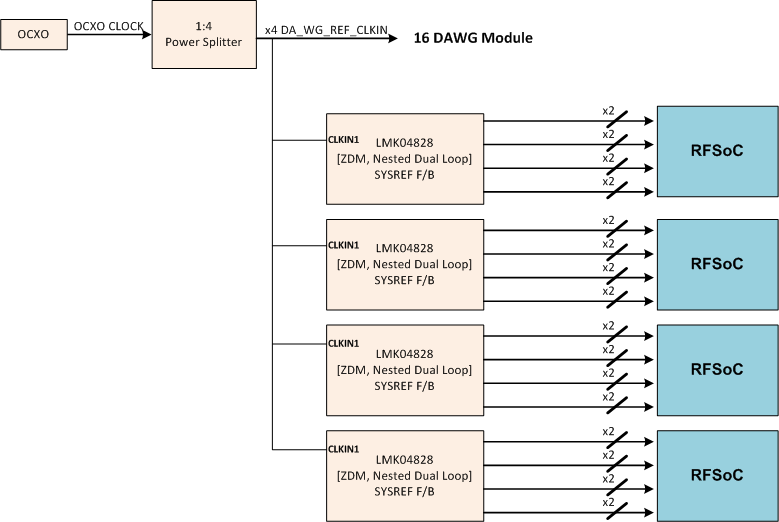

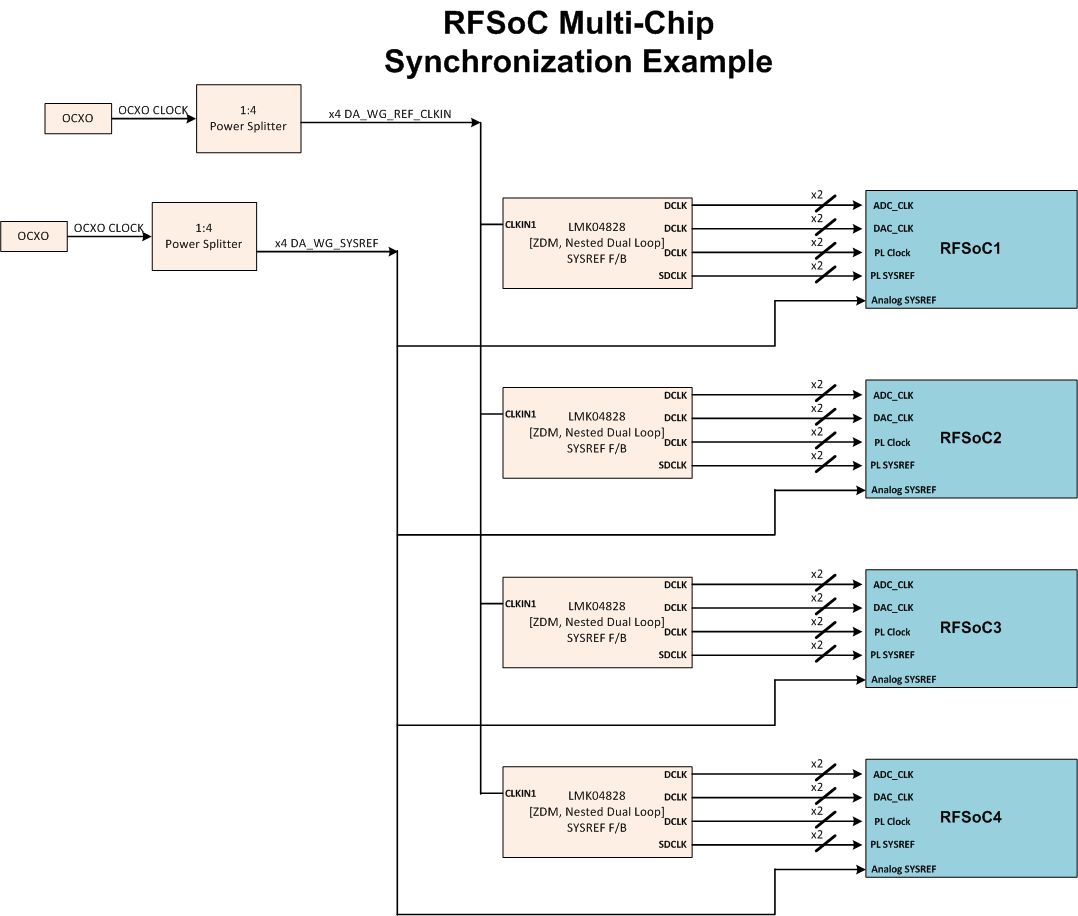

We are developing Zynq RFSoC based board for 64CH ADC sampling. For the same, we are using 4 RFSoC boards each with LMK04828 CLK synthesizer.

The CLKIN for all the LMKs is from single oscillator source.

Since we need to sample all ADC channels with as less as possible phase delay, so could you let us know how to SYNC multiple LMK04828